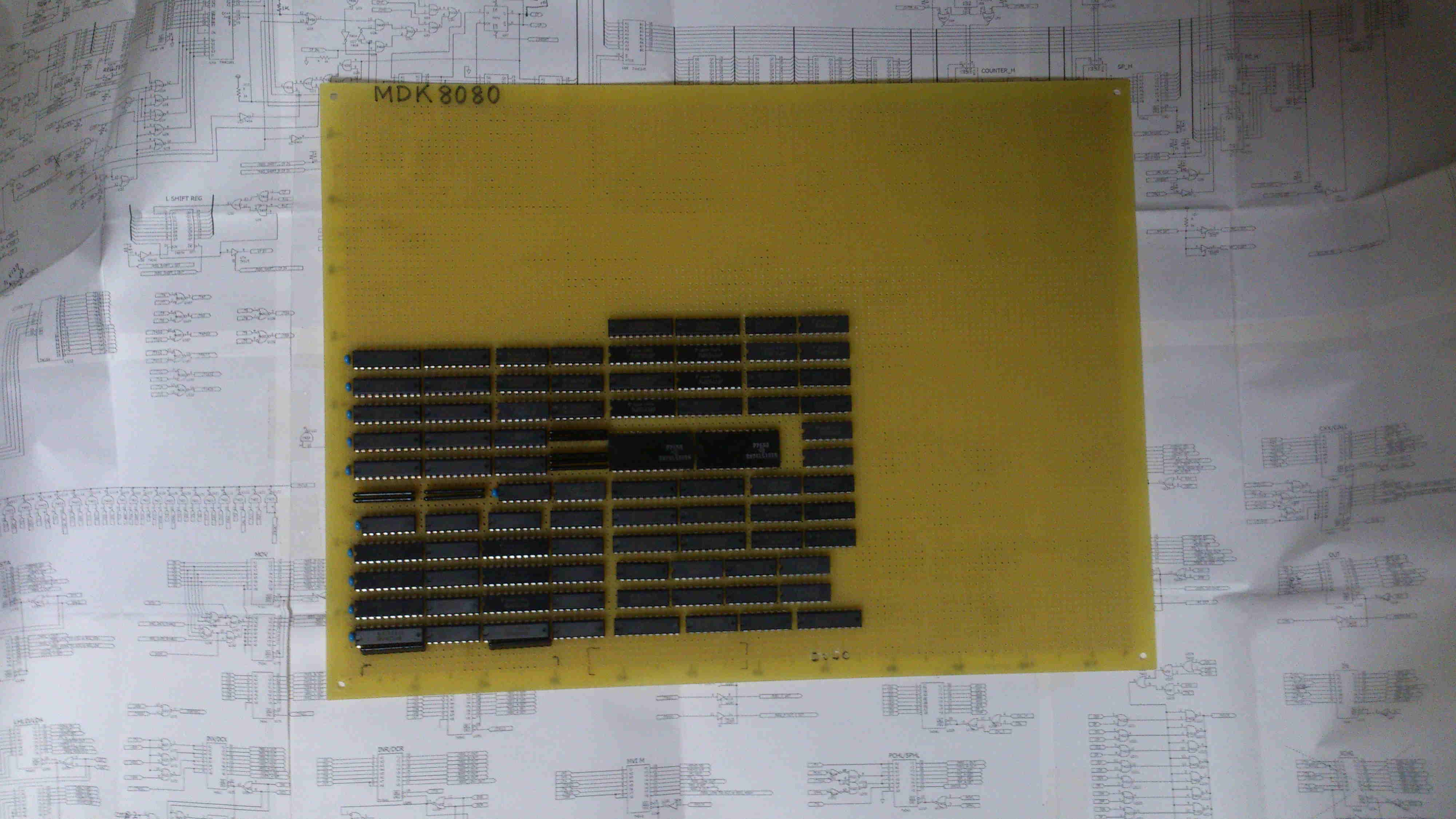

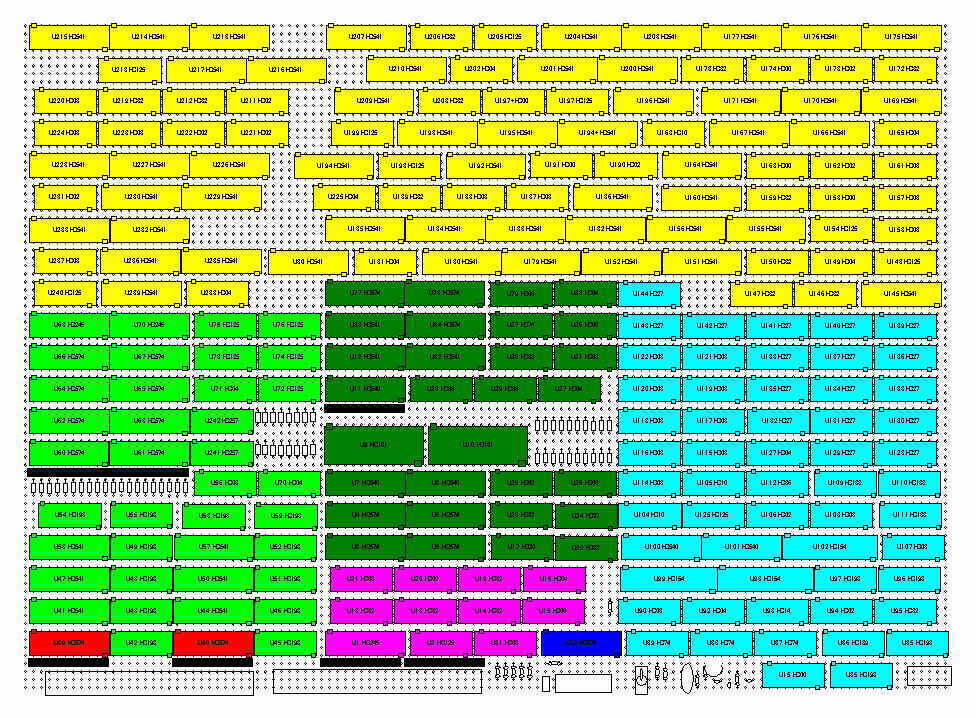

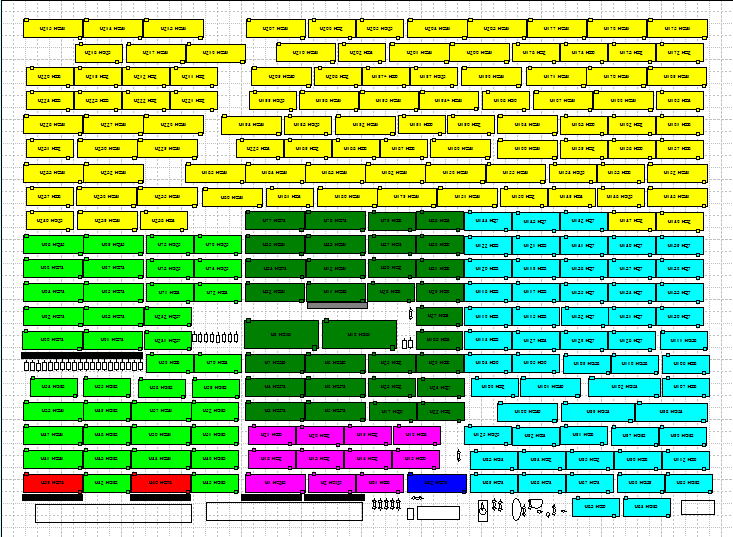

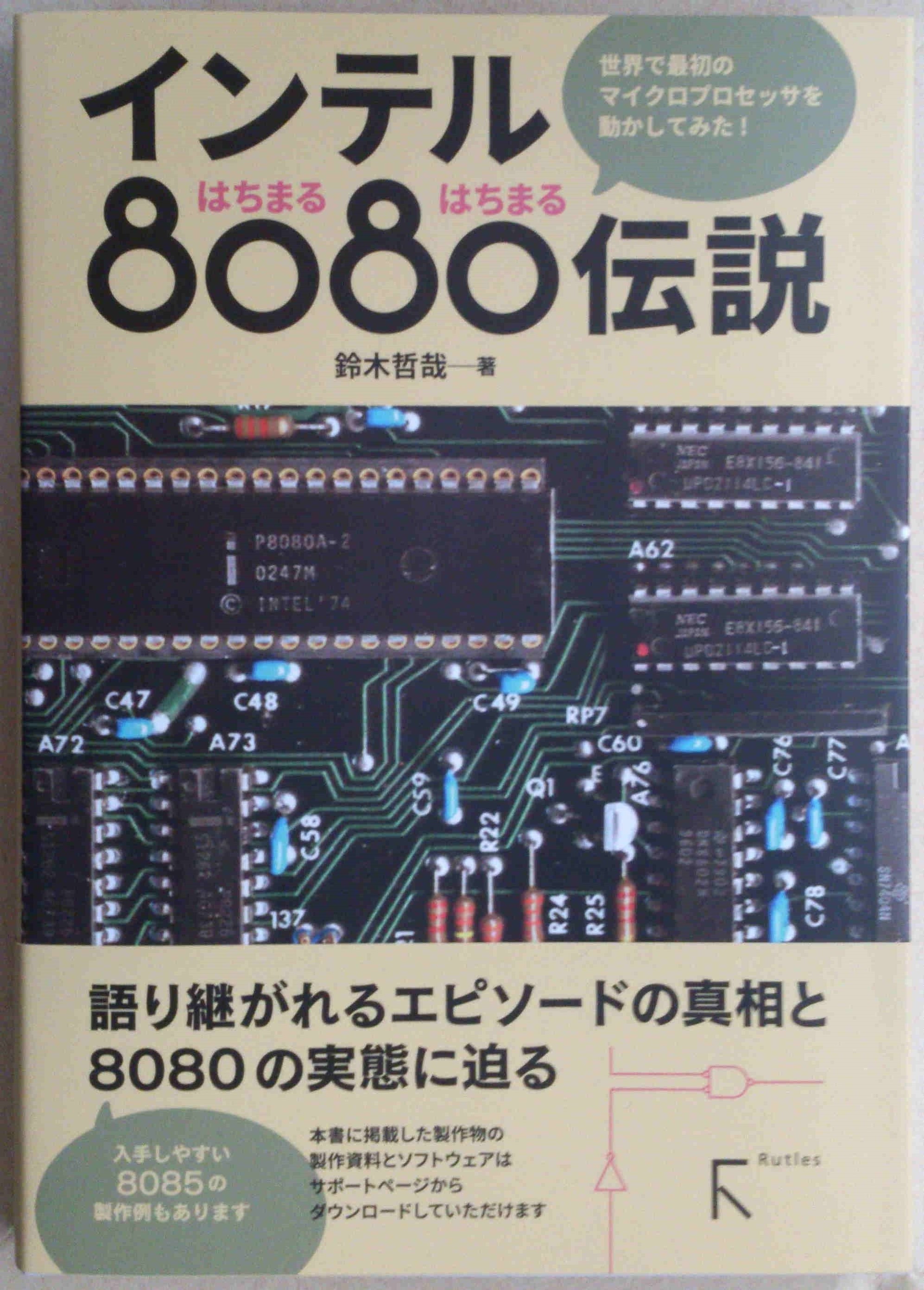

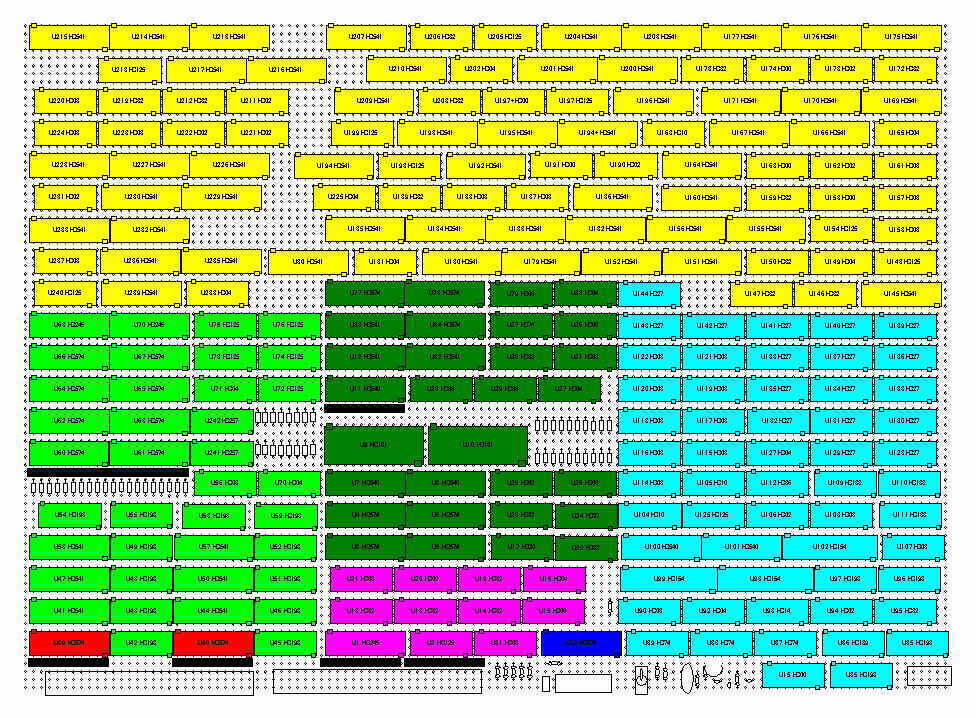

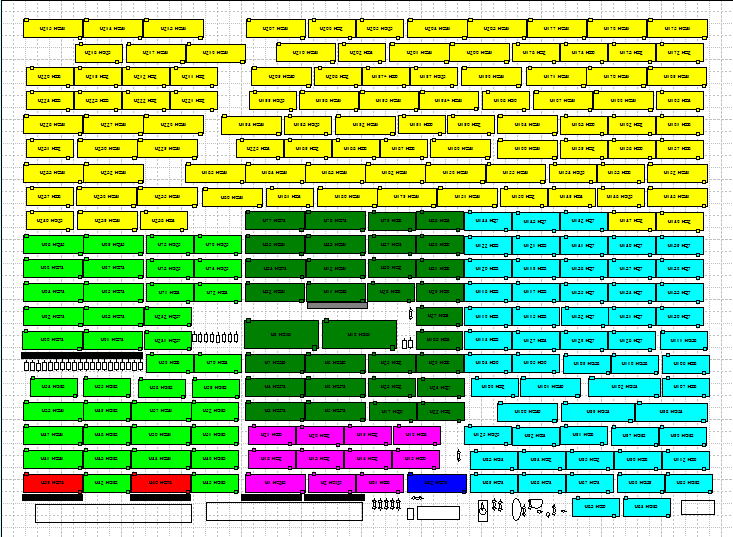

儅僀僐儞偺惢嶌乮帺嶌俠俹倀丂俉侽俉侽乯

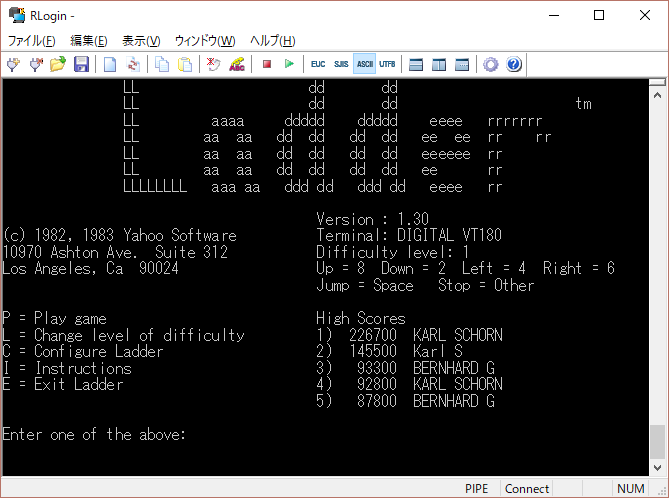

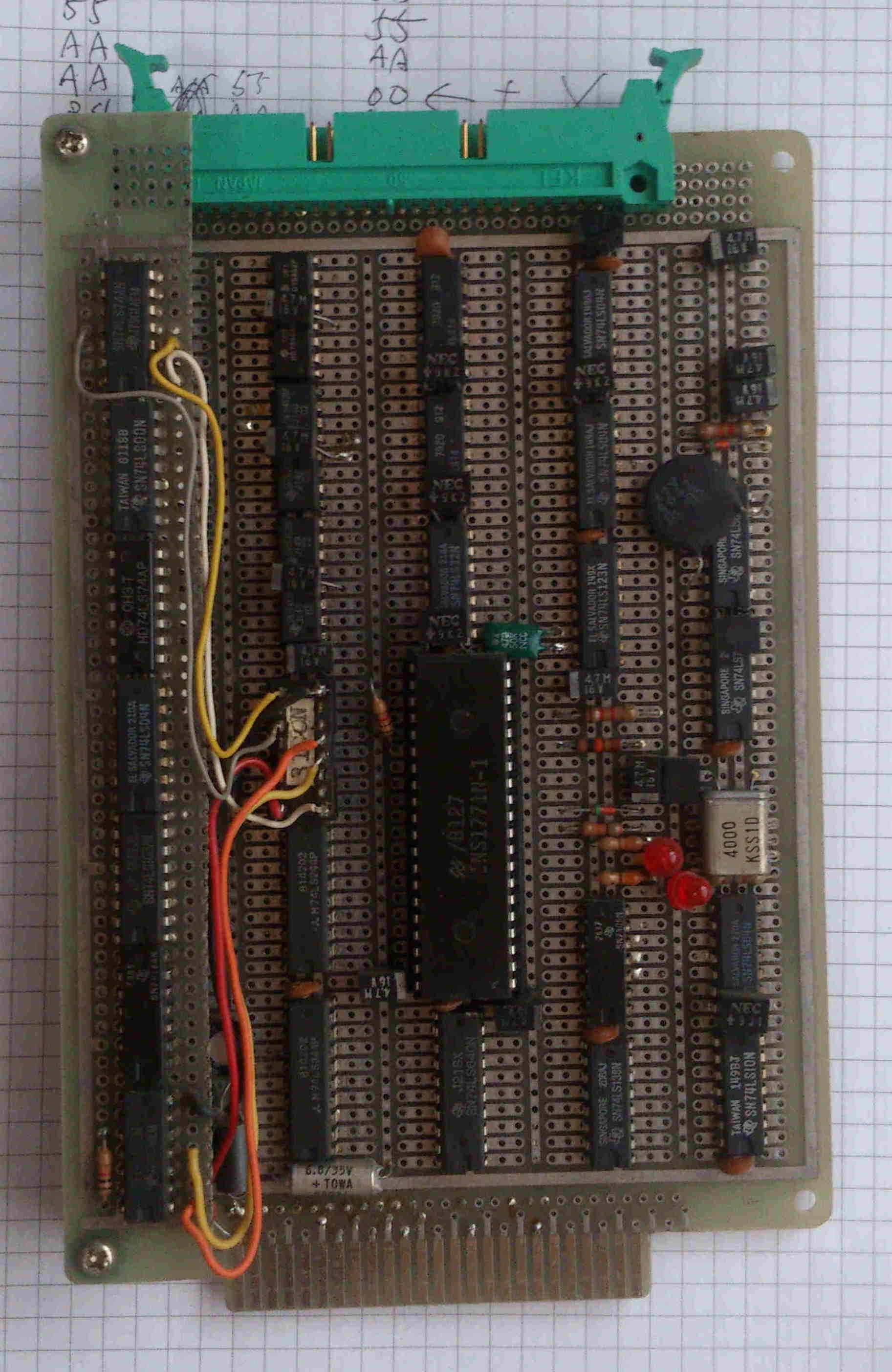

乮俈係俫俠乮俴俽傕偁傞乯僔儕乕僘偺俢俬俹偱俉侽俉侽傕偳偒傪惢嶌丅柤徧傪俵俢俲俉侽俉侽偲偟偨丅乯

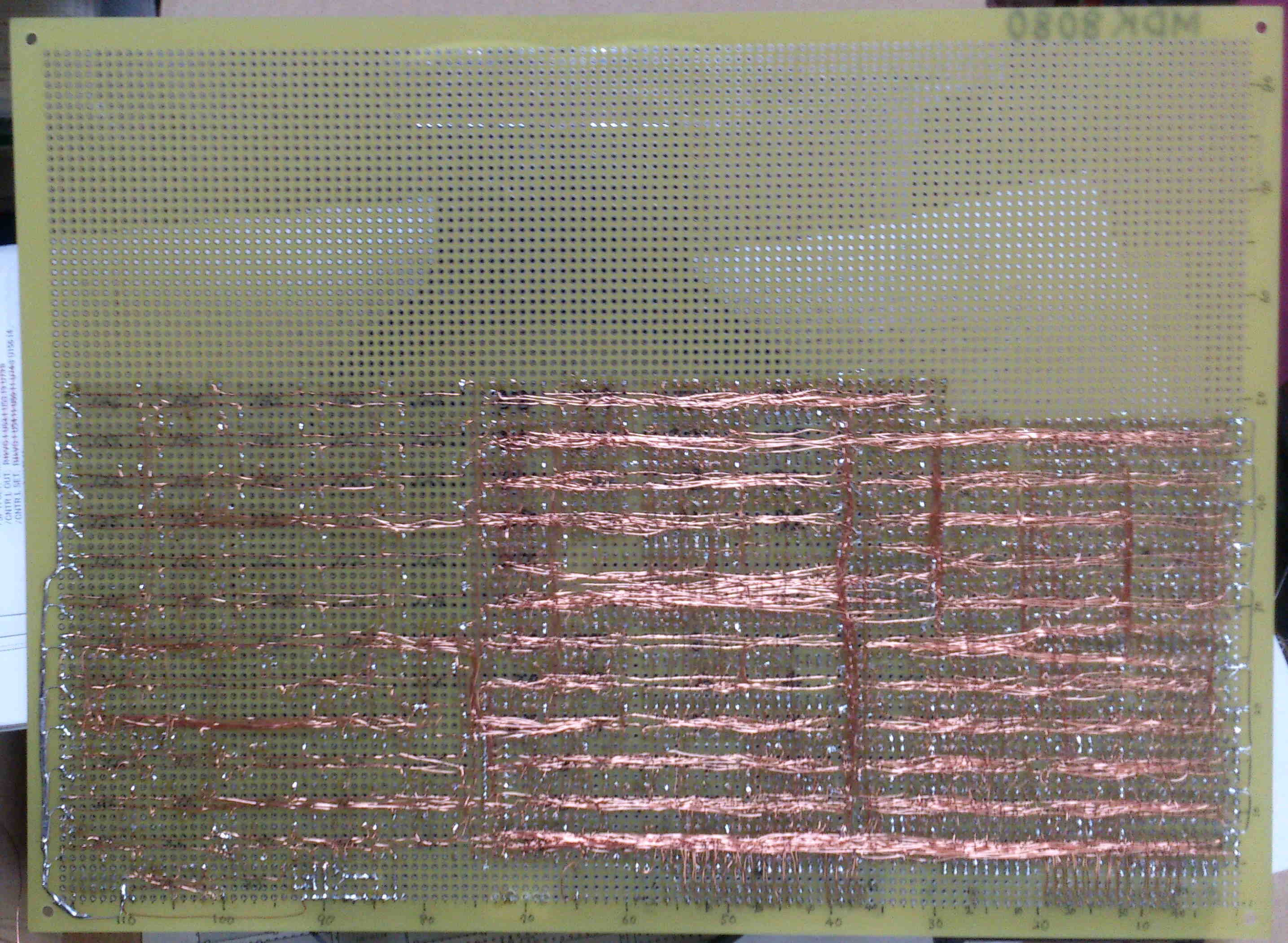

俀侽侾俇擭侾侾寧

侾丏丂偼偠傑傝

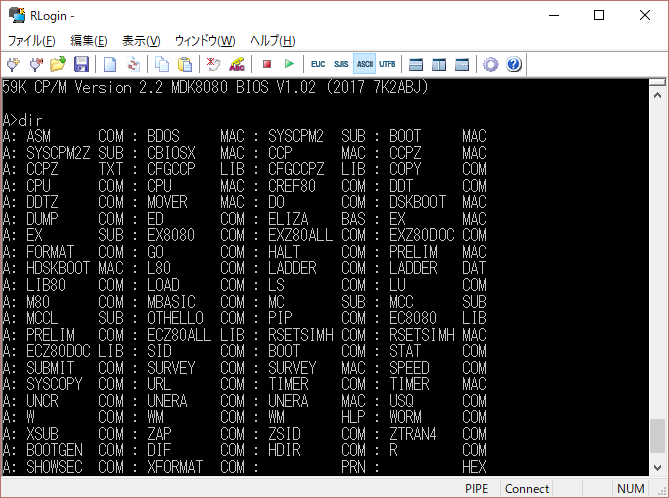

丂僾儘僼傽僀儖偺偲偙傠偱儅僀僐儞偺偙偲傪彂偄偨偺偱巚偄弌偟偨偑丄俙倢倲倎倝倰俉俉侽侽偺傛偆側僐儞僺儏乕僞傪嶌傠偆偲偟偨嶌傝偐偗偁偭偨偼偢偲墴擖傟傪扵偟偰傒偨丅偱傕尒偮偐傜側偐偭偨丅偳偆偟偨偺偐側偁丅丠両偦偆偩丄尰嵼偺偲偙傠偵堷偭墇偟偨帪偵丄僈儔僋僞攑婞柦椷偱攑婞偟偨偐傕偟傟側偄丅偟傑偭偨丅幪偰側偗傟偽傛偐偭偨丒丒丒丒丅

丂夰偐偟偔側傝僱僢僩偱俉侽俉侽傪専嶕偡傞偲丄偁傞偁傞丄傒側偝傫俉侽俉侽傕偳偒傪惢嶌偟偰俠俹乛俵傑偱堏怉偟偰偄傞傛偆偩丅偦偺側偐偱傕拞擔揹岺偝傫偺儁乕僕偑埑姫偩偭偨丅側傫偲俿俿俴乮幚嵺偼俈係俫俠乯偱俉侽俉侽俠俹倀傪嶌傞偲尵偆偺偱偁傞丅婰帠傪撉傫偱偄傞偆偪偵嶌傝偨偔側偭偨丅弌棃偨偲偟偰壗偵巊偆偐丄壗偵偮偐偊傞偐丠側偳偲巚偭偨偑丄偦傫側偙偲傪峫偊傞偲庯枴側傫偰偱偒側偄丅偙傟偼儘儅儞偱偁傞丅偱傕慻傒棫偰傞偩偗偱偼偮傑傜側偄乮揤幾婼偩偹偉乯丅慻傒棫偰傞偺偱偼側偔憂傞偺偱偁傞丅帺暘偱夞楬傪峫偊偰摦偐偡偺偑妝偟偄偺偱偁傞丅

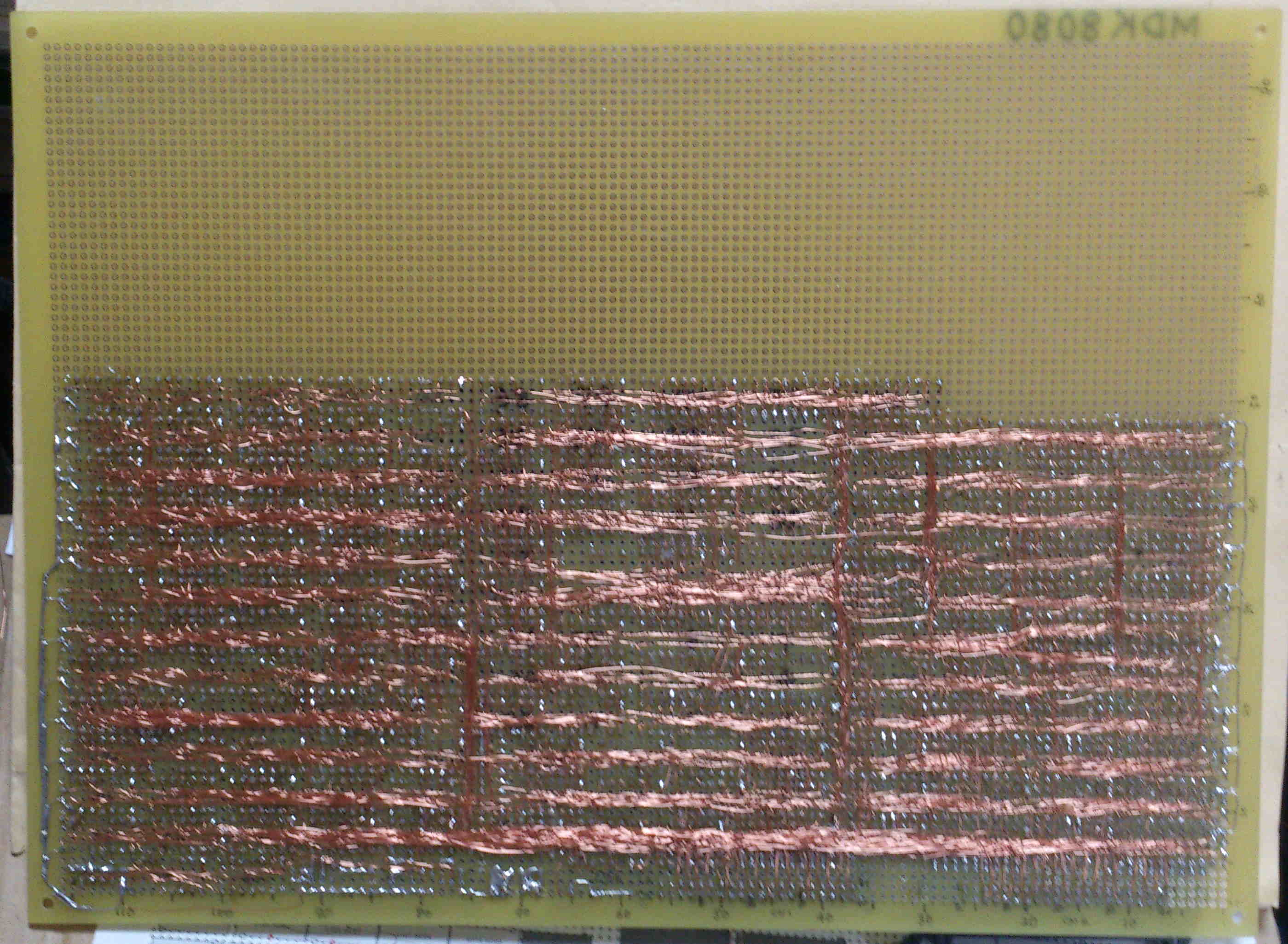

俀侽侾俇擭侾俀寧

俀丏丂夞楬愝寁

丂帺暘偱夞楬傪峫偊傛偆偲堄婥崬傫偱傒偨傕偺偺丄偼偨偟偰夞楬偑偱偒傞偺偐丅傑偢偼俠俹倀偺巇條傪扵偟偨丅98-153B_Intel_8080_Microcomputer_Systems_Users_Manual_197509偲尵偆惵偄昞巻偺帒椏偑僟僂儞儘乕僪偱偒偨丅曋棙側悽偺拞偩丅

丂偱傕俙俴倀偑庤偵擖傞偺偐丠丄拞擔揹岺偝傫偼壛嶼婍傪巊偭偰偄偨偑丅俙俴倀偺俈係俫俠侾俉侾傪扵偡偲拞崙偵偁偭偨丅偲傝偁偊偢拲暥偩偗偟偰偍偄偨丅俙俴倀偑擖庤偱偒傞偮傕傝偱夞楬傪峫偊傞偙偲偵偟偨丅

丂俉侽俉侽偺柦椷偼侾俇恑悢偱昞尰偝傟偰偄傞偑丄儗僕僗僞偼俈屄亄侾側偺偱丄僆儁儔儞僪偼俁倐倝倲偱偁傞丅偙傟偼俹俢俹亅侾侾偲摨偠傛偆偵俁倐倝倲偱嬫愗偭偨曽偑暘偐傝傗偡偄丅柦椷僨僐乕僪偼俁倐倝倲偱嬫愗偭偰僨僐乕僪偡傛偆偵偡傞丅

丂俵俤俵俷俼倄偺俼俤俙俢丄倂俼俬俿俤偲俬俷偼暘棧偟偰弌偡傛偆偵偡傞丅偮傑傝俉侽俉侽亄俉俀俀係亄俉俀俀俉偑堦懱偵側偭偨夞楬偲偡傞丅

丂栺侾儠寧偐偐偭偰夞楬偑弌棃偨丅摢偺拞偱偼摦嶌偟偰偄傞乮偄偮傕偦偆偩偑丄尰幚偼堘偆丒丒丒娋乯丅偱傕俙俴倀偑撏偐側偄丅侾儠寧宱偮偺偩偑丅栤偄崌傢偣偨傜丄搑拞偱暣幐偟偨傛偆側偺偱嵞搙憲傞偲楢棈偑棃偨丅偝偡偑拞壺丒丒丒丒丅傕偆侾儠寧懸偨偹偽丅

夞楬恾丂丂丂丵丵丵

偱傕偳偆傗偭偰婎斅傊偮偗傞偐丠丅廐寧偵儐僯僶乕僒儖婎斅偺俙係乮傛傝偪傚偭偲戝偒偄乯僒僀僘偑偁傞偺偑暘偐偭偨丅偙傟偵嵹傜側偗傟偽偁偒傜傔傛偆丅恾柺傪昤偄偰傒偨丅

偍傗偍傗偆傑偔嵹偭偰偟傑偭偨丅彮偟梋桾偑偁傞丅偁偲俀乣俁屄俬俠傪嵹偣傟傞丅夞楬僨僶僢僌偱俬俠偑捛壛偵側偭偰傕壗偲偐側傝偦偆偩丅偮傑傝嶌傟偲偄偆揤偺惡偐丒丒丒丒丅

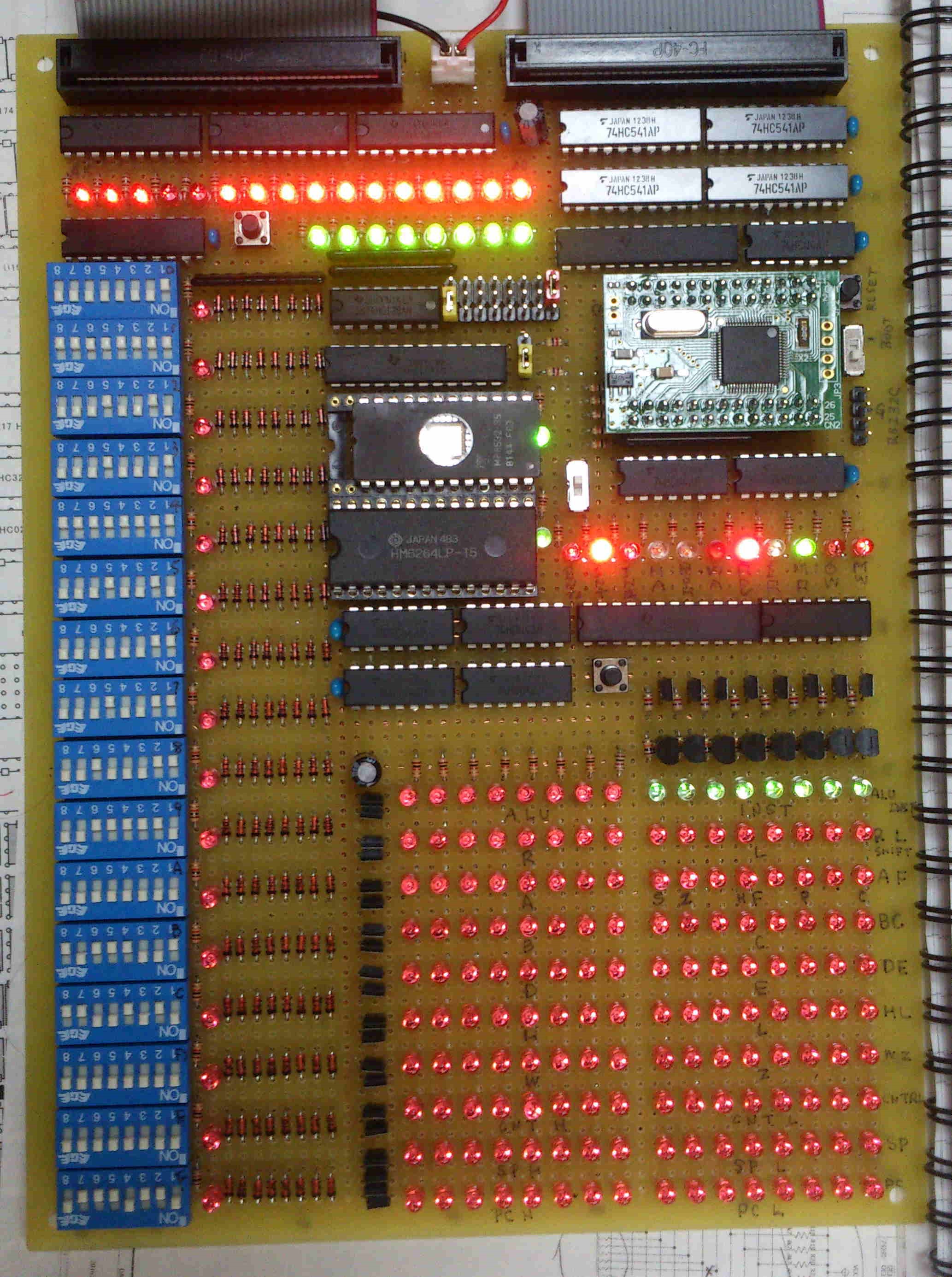

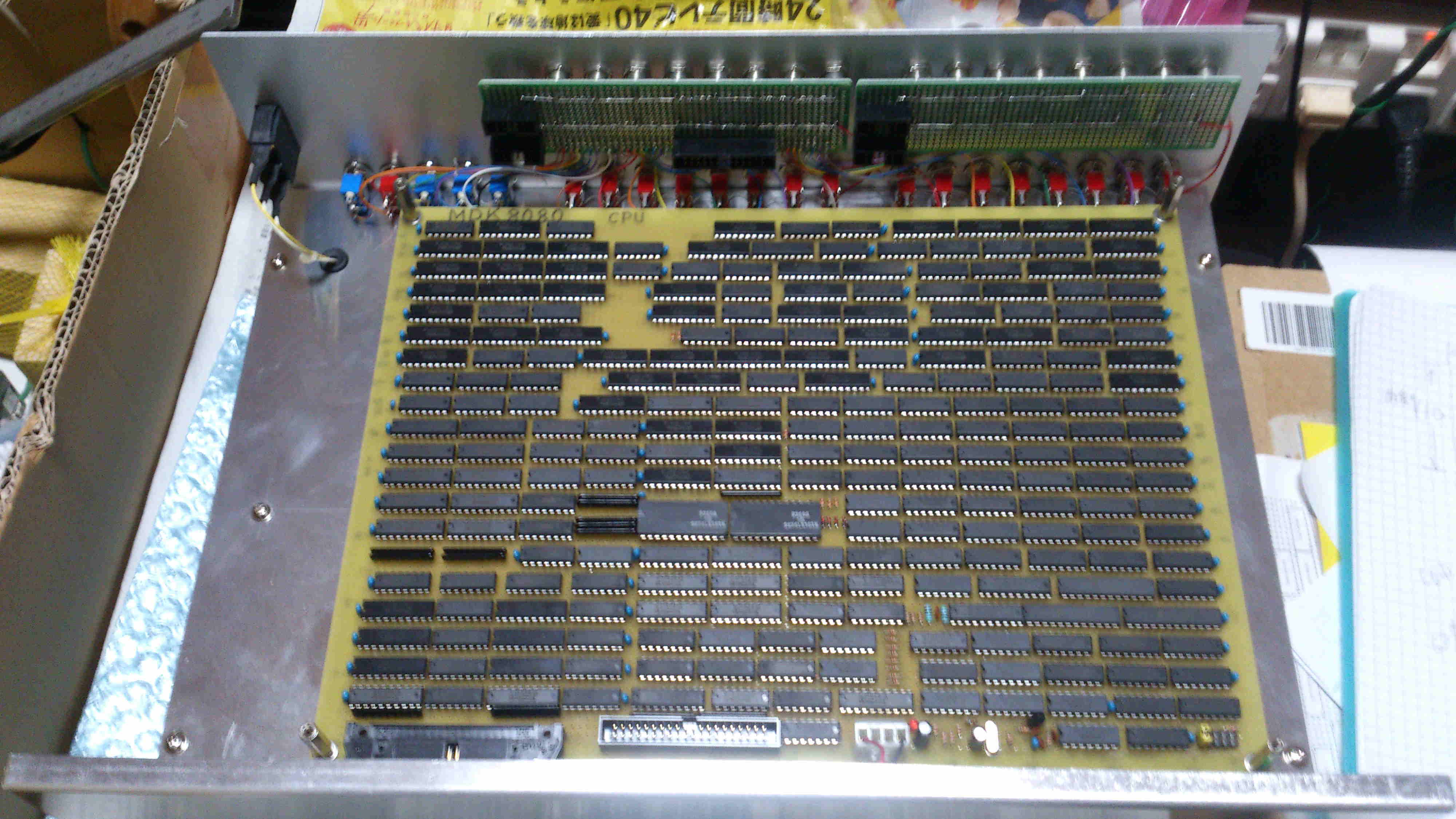

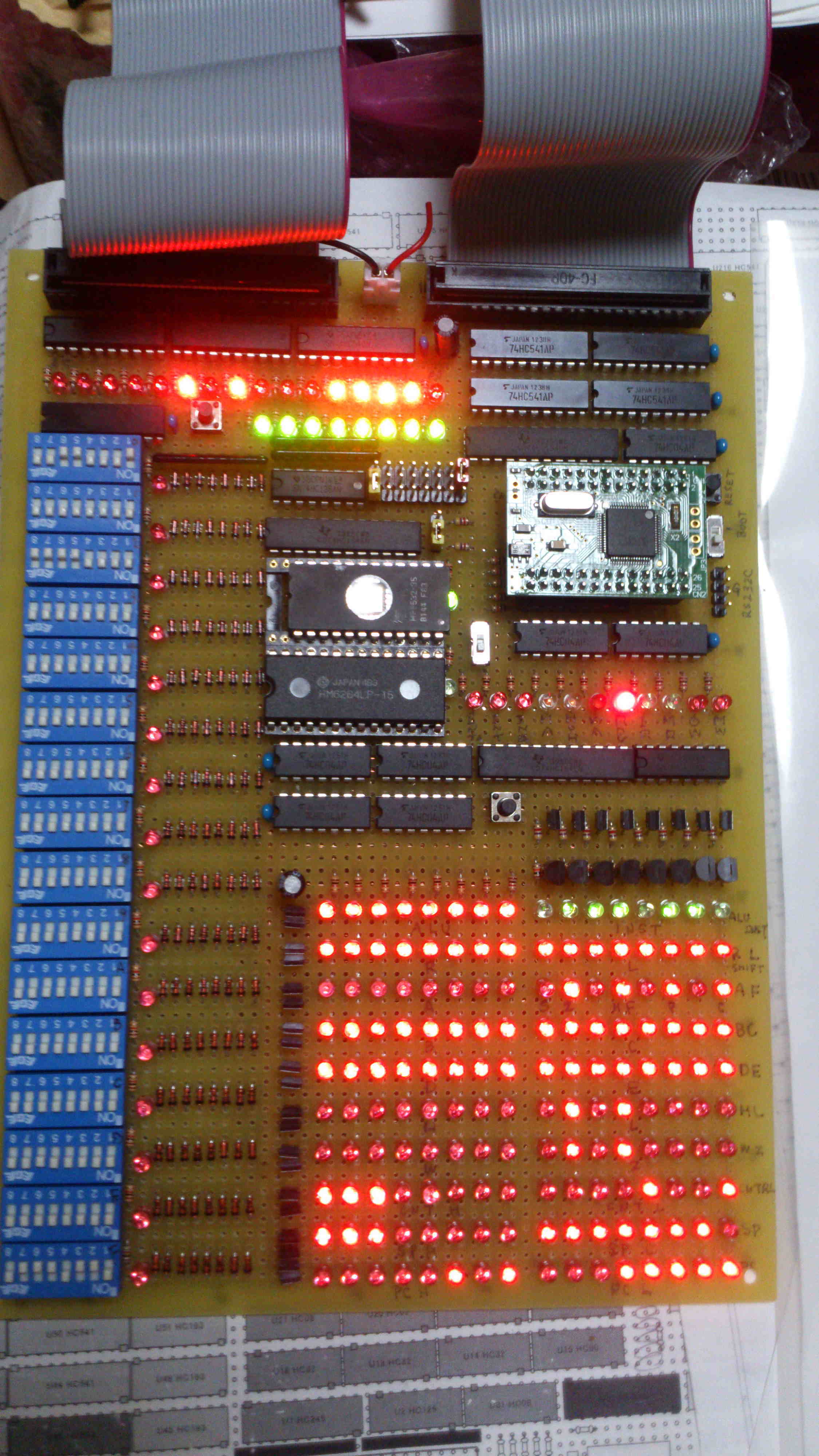

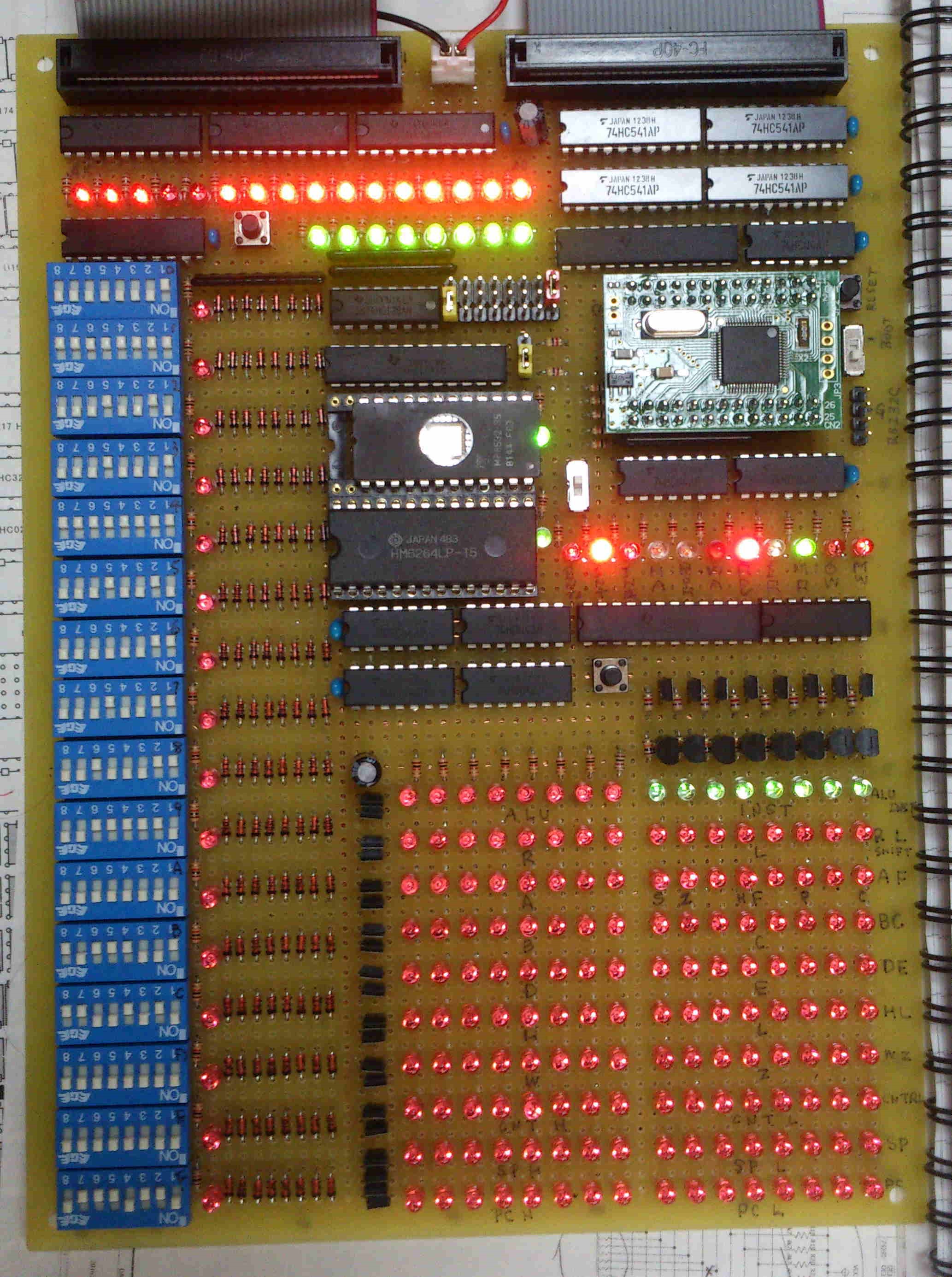

偪側傒偵愒偑傾僪儗僗儗僕僗僞丅墿椢偑僾儘僌儔儉僇僂儞僞傗僗僞僢僋億僀儞僞丄俫俴側偳偺儗僕僗僞晹暘偱偁傞丅椢偼俙儗僕僗僞傗僼儔僌儗僕僗僞丄俙俴倀丄僔僼僩梡儗僕僗僞側偳丄僺儞僋偼儊儌儕乕俼俤俙俢丄倂俼俬俿俤丄俬俷丂俼俤俙俢丄倂俼俬俿俤側偳偺怣崋晹丄惵偑柦椷儗僕僗僞丄悈怓偑僋儘僢僋偲柦椷僨僐乕僪晹丄墿怓偑柦椷幚峴晹偱偁傞丅

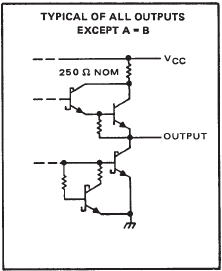

ALU廃傝偺夞楬傪峫偊傞偲偒偵丄ALU偺巇條傪専摙偟偨偑丄僨乕僞偼晧榑棟偱愝寁偝傟偰偄傞丅偟偐偟丄偦偺傑傑偺摦嶌偱惓榑棟偱庴偗庢傞偙偲傕偱偒傞丅俈係HC181偼榑棟傪愗傝懼偊偰壛嶼丄尭嶼丄AND丄OR丄XOR側偳偦偺傎偐偺儘僕僢僋傕摦嶌偡傞丅偦偺懠偺儘僕僢僋偺偲偒偵惓榑棟偺摦嶌傕偱偒傞傛偆偩丅偟偐偟丄撪晹摍壙夞楬傪尒傞偲A=B偺怣崋偼晧榑棟偱側偄偲偆傑偔摦嶌偟側偄傛偆偵尒偊傞丅愢柧彂偵偼惓榑棟偺応崌偳偆側傞偐柧婰偝傟偰偄側偄丅帠慜偵挷傋偨偄偑丄拞壺偐傜偼傑偩撏偐側偄丅傂傚偭偲偡傞偲塱媣偵撏偐側偄偐傕偟傟側偄丅帠慜偵挷傋偨偄偺偲曐尟偵偲暿搑扵偡偙偲偵偟偨偑丄傗偼傝柍偄傛偆偱偁傞丅柍偄偲偄偆偺偼娫堘偄偱偁傞偲偙傠偵偼偁傞偑丄侾侽侽屄攧傝偱侾屄攧傝偼偟偰偄側偄丅侾侽侽屄傕偄傜偄側偄偺偱偦偙偼僟儊偱偁傞丅偱偼丄俈係LS181偼偲挷傋傞偲丄偙傟偼傑偩巆偭偰偄傞傛偆偱丄俀屄傎偳峸擖偟偨丅嵟埆ALU偩偗俈係LS侾俉侾偵偡傞偙偲偵偡傞丅

丂偝偭偦偔ALU偺幚尡傪傗偭偰傒偨丅傗偭傁傝A=B偼晧榑棟偺偲偒偩偗惓偟偔摦嶌偡傞丅側偺偱晧榑棟偱夞楬傪愝寁偟偨丅

俀侽侾俈擭侾寧

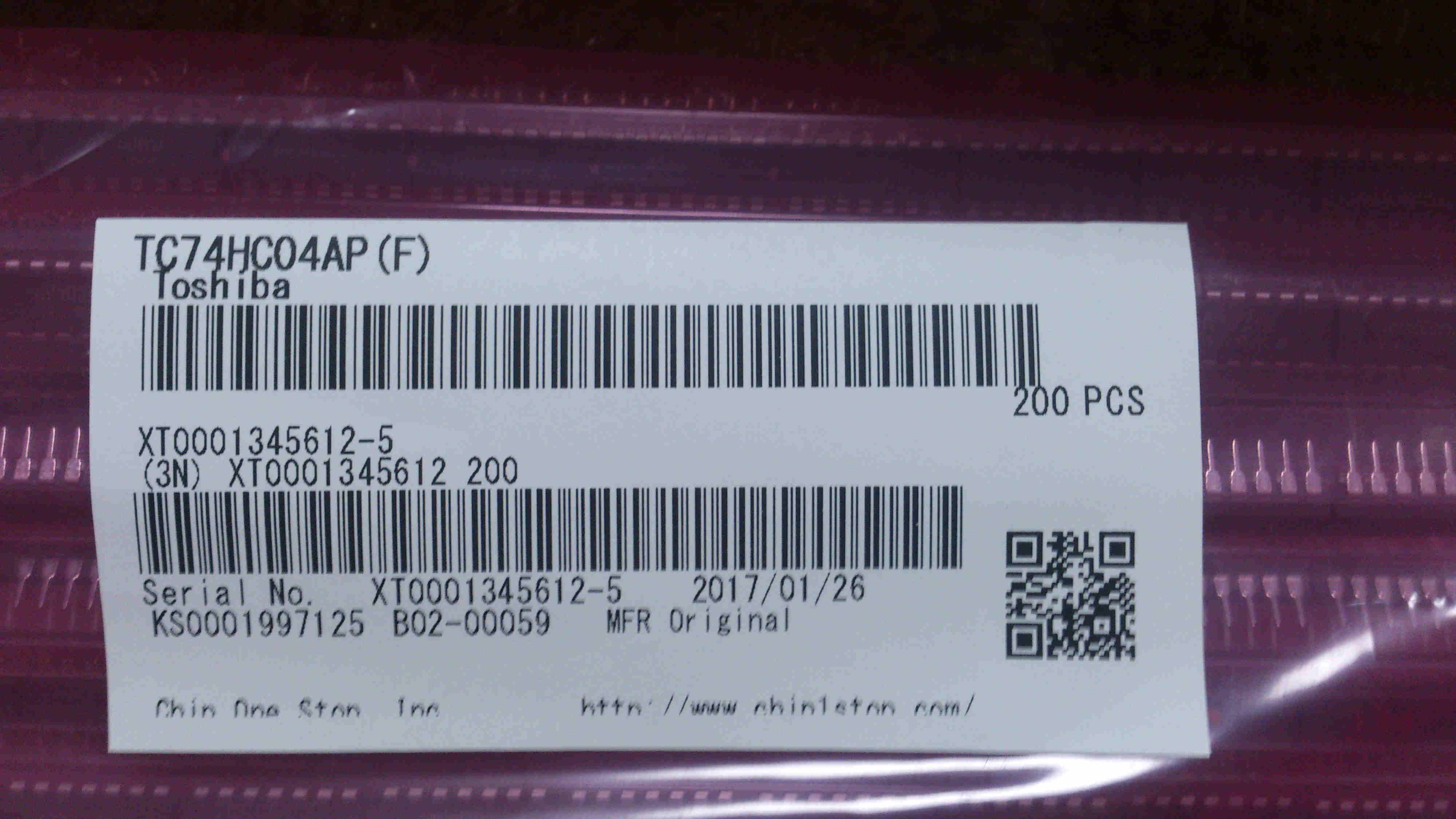

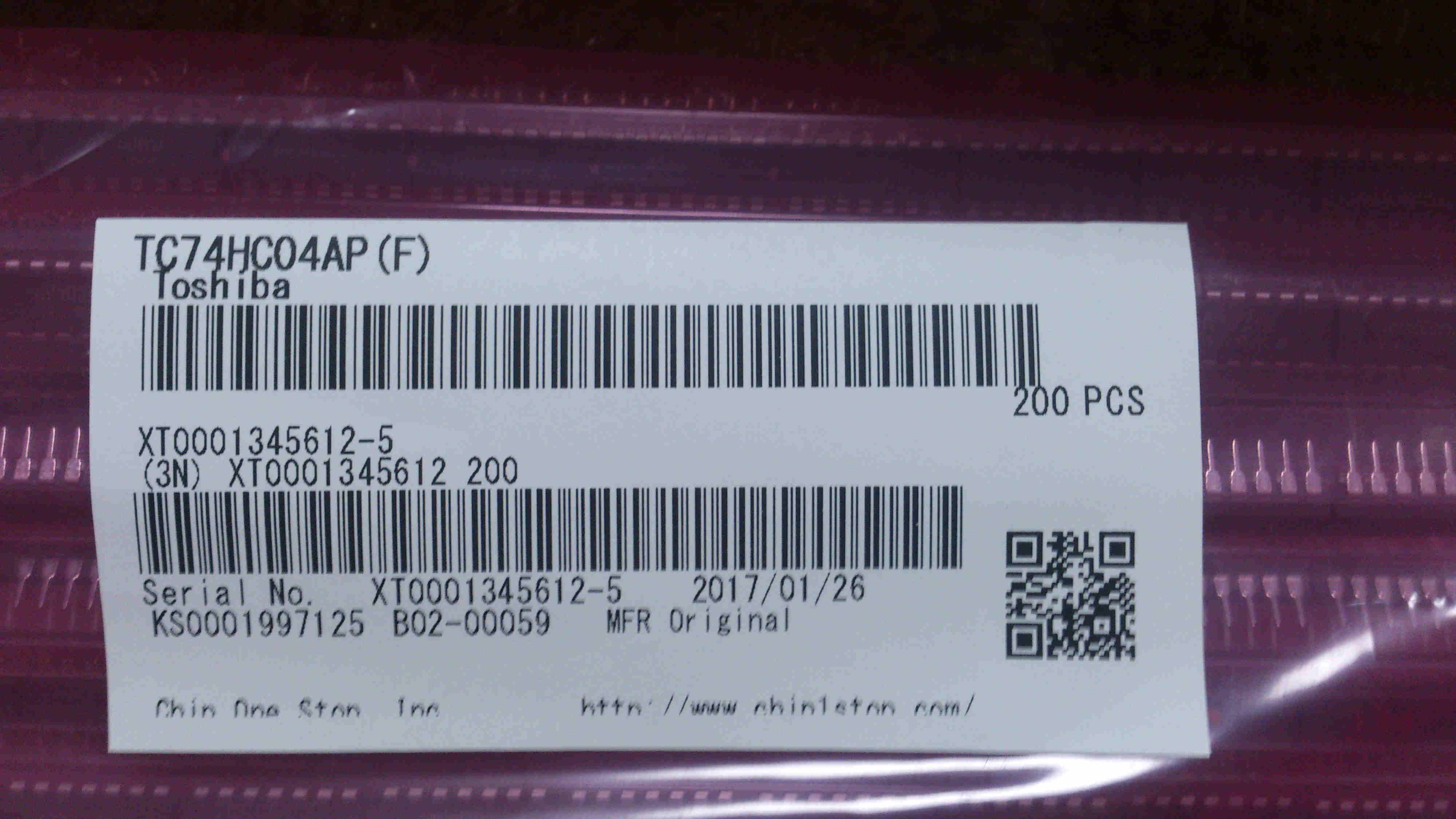

丂敪拲偟偰偄偨IC乮堦晹乯偑倎倝倲倕値倓倧偐傜撏偄偨丅

倎倝倲倕値倓倧偝傫丄偍婅偄偱偡偐傜俬俠偼摫揹僗億儞僕偵偝偟偰壓偝偄丅

俀侽侾俈擭侾寧

丂巆傝偺俬俠偑們倛倝倫侾倱倲倧倫偐傜撏偄偨丅崼曪偼偝偡偑丄摫揹僗億儞僕傗俬俠梡儗乕儖偵擖偭偰偄傞丅

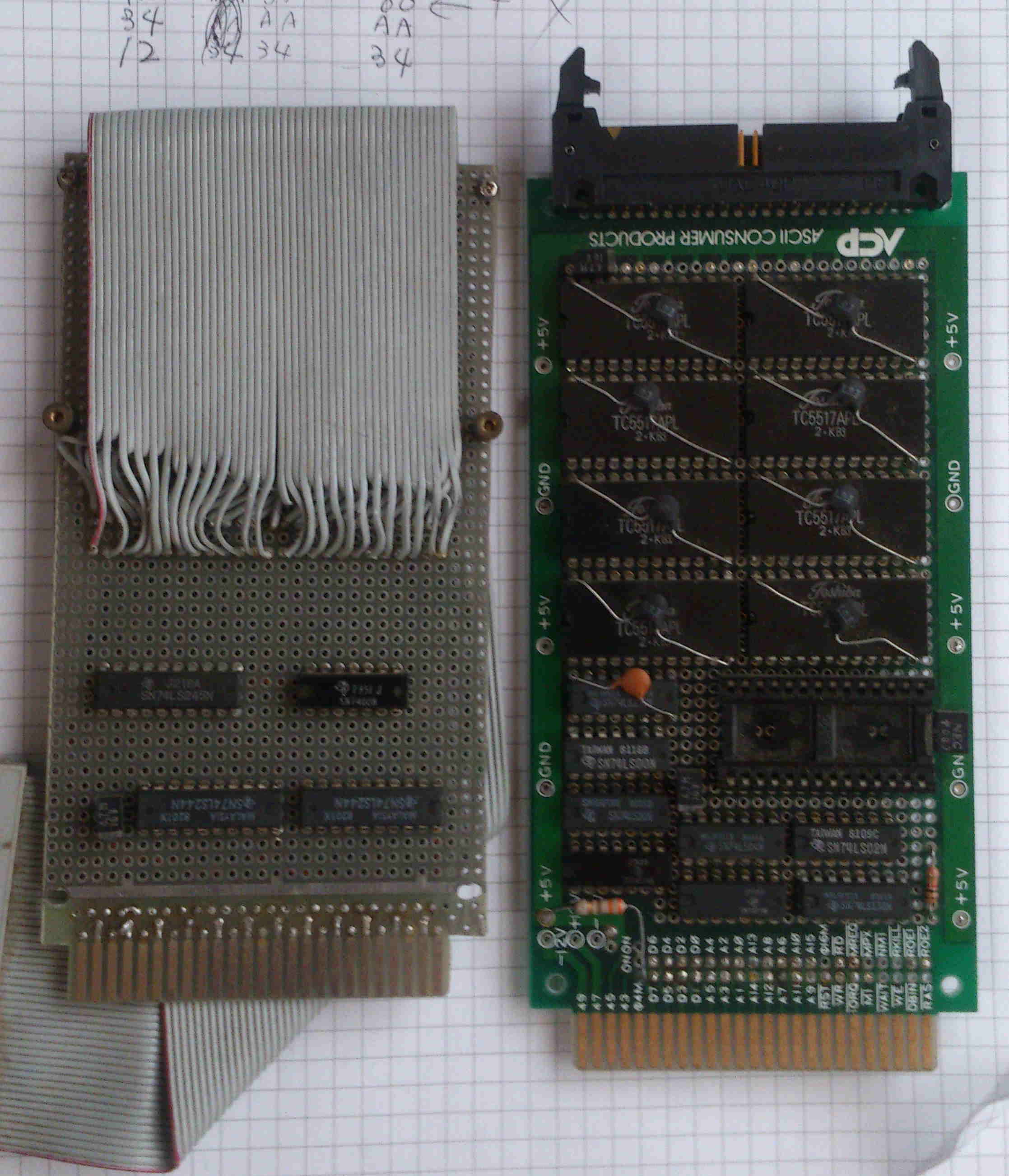

埑姫偼偙傟偐側丅俈係俫俠侽係偑俀侽侽屄偱偁傞丅俀侽侽屄埲忋偱偺斕攧偩偭偨丅偱傕偙傟偱侾俁侾墌偱偁傞丅嵼屔張暘偐側丠

俀侽侾俈擭侾寧

丂崱擔壗婥偵夞楬傪傒偰偄傞偲俢俙俙偺寁嶼夞楬傪娫堘偭偰偄傞偺偵婥晅偄偨丅側傫偱娫堘偭偨偐側偀丅俙俴倀夞傝傪惓榑棟偐傜晧榑棟夞楬偵曄峏偟偨偲偒偵傕傟偨偐側偀丅俬俠偑偦傠偭偨偟乮僐僱僋僞椶偼傑偩偩偑乯丅偦傠偦傠嶌傝偼偠傔傞偐側丅偳偺偔傜偄妡偐傞偩傠偆丅俀侽俹俬俶偲侾俇俹偲侾係俹偩偑俀侽俹偑懡偄丅偍偍偞偭傁偵俀侽俹偑俀侽侽屄偲偟偰係侽侽侽杮偺攝慄偐側丅

丂偊偭丒丒丒丅偦偆偄偆寁嶼偱偼柍偄偭偰丒丒丒丅偦偆偩偗偳丒丒丒丅俬俠偺僺儞俁杮傪宷偖攝慄偼俀杮偺寁嶼偩偐傜偱偡偹丅偱傕僐儞僨儞僒傗僾儖傾僢僾掞峈傗傜傪宷偖偺偱偦傟傪娷傔偰丄偍偍偞偭傁偵寁嶼偟偰偄傞偺偱偡丅

丂係侽侽侽杮偩偲偡傞偲係侽杮乛擔偲偡傞偲侾侽侽擔偐偐傞丅俁儠寧傎偳偐偐傞偐側偀丅偡傞偲俆寧偺楢媥偵僥僗僩奐巒偱偒傞偐側丠

丂偱偼丄偦傟傪栚昗偵偑傫偽傠偆両

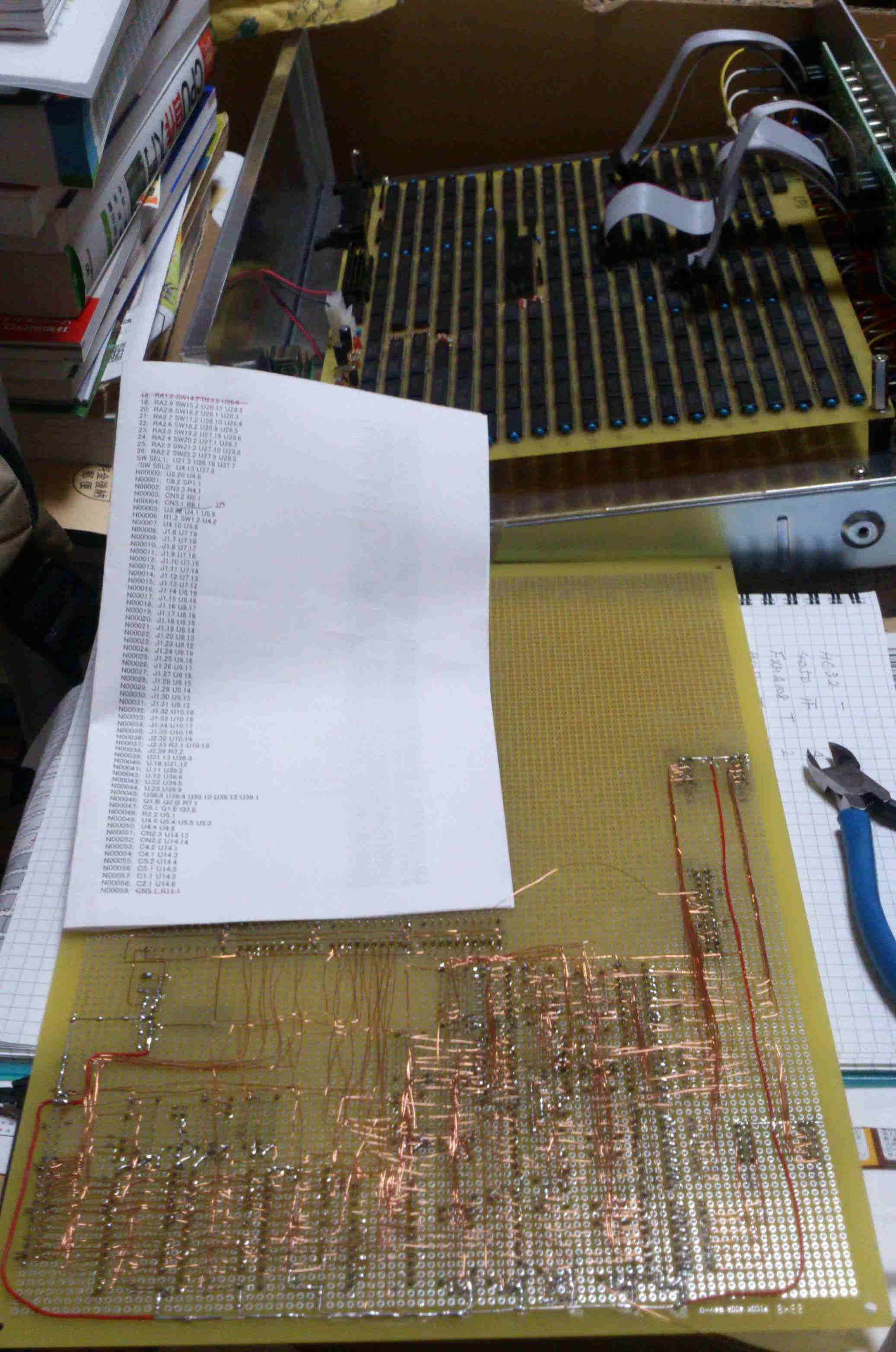

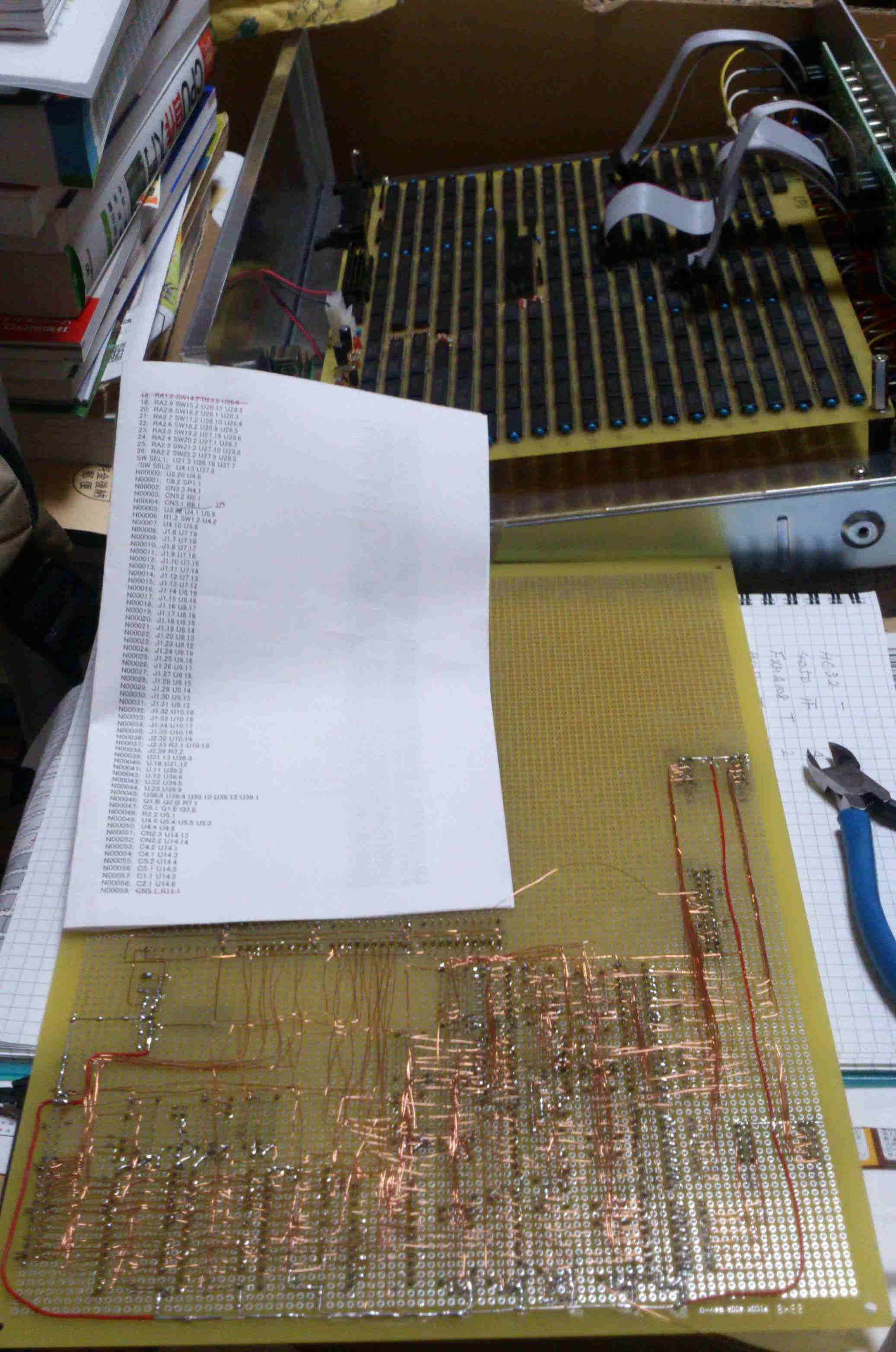

俀侽侾俈擭俀寧

丂嵟廔僠僃僢僋偲巚偭偰側偵偘偵夞楬恾傪傒偰偄傞偲丄俬俠斣崋偵僟僽傝偑偁偭偨丅傗傟傗傟丄俬俠傪侾屄捛壛偩丅偍傗乕乕丄斣崋偵嬻偒偑偁傞丅偳偆傗傜僐僺乕屻偺曄峏朰傟偐丠丅斣崋傪庢偭偰偄傞偺偱曄峏朰傟偼側偝偦偆偩偑丒丒丒偼偰丠丅偄偢傟偵偟傠攝抲恾傪廋惓偣偹偽丅偍傗丄攝抲恾偵傕娫堘偄偑丒丒丒丅僐僺乕偟偰攝抲偟偰斣崋傪彂偒姺偊傞偺朰傟偰偄傞丅傗傟傗傟抪偢偐偟偄攝抲恾傪傾僢僾偟偰偟傑偭偨丅

廋惓偟偨攝抲恾

俀侽侾俈擭俀寧

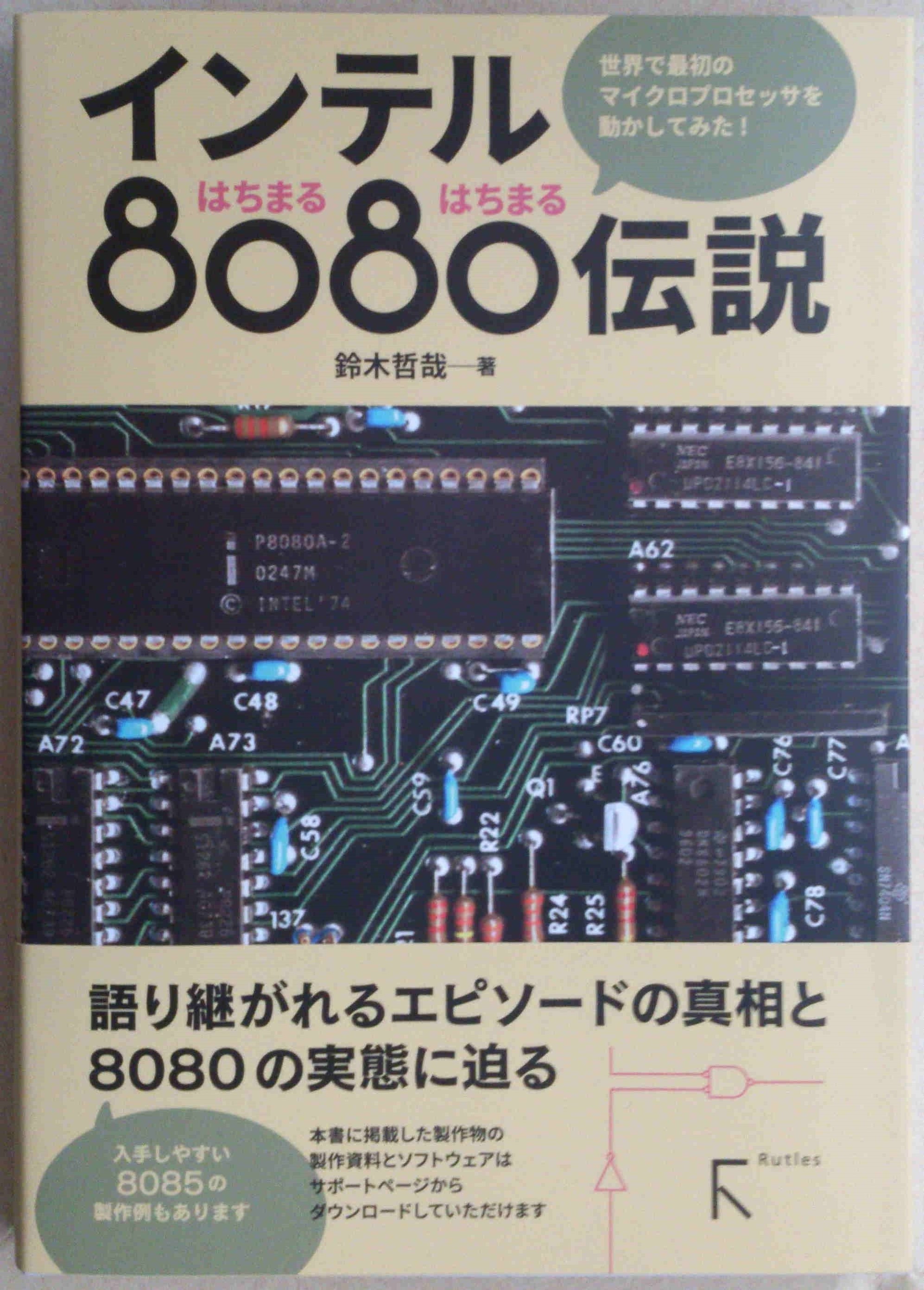

丂偁偁丄偦偆偦偆丅夞楬愝寁偡傞偵偁偨傝丄杮扞偺旍傗偟偵側偭偰偄偨偙偺杮傪堷偭挘傝偩偟偰嶲峫偵偟偨丅栺係侽擭慜偵俠俹倀傪嶌傠偆偲偟偰攦偭偨杮偱偁傞丅巇帠偱僐儞僺儏乕僞傪偝傢偭偰偄偨偣偄傕偁傞偐傕偟傟側偄偑丄寢嬊姰惉偟側偐偭偨丅Profile偵彂偄偨偑丄TMS俉侽俉侽傪巊偭偨晹昳僉僢僩傪嶌偭偨偩偗偱撢嵙偟偰偄偨偺偩丅係侽擭宱偭偰傛偆傗偔嶌傞偙偲偵側傠偆偲偼丅

丂

丂

俀侽侾俈擭俀寧

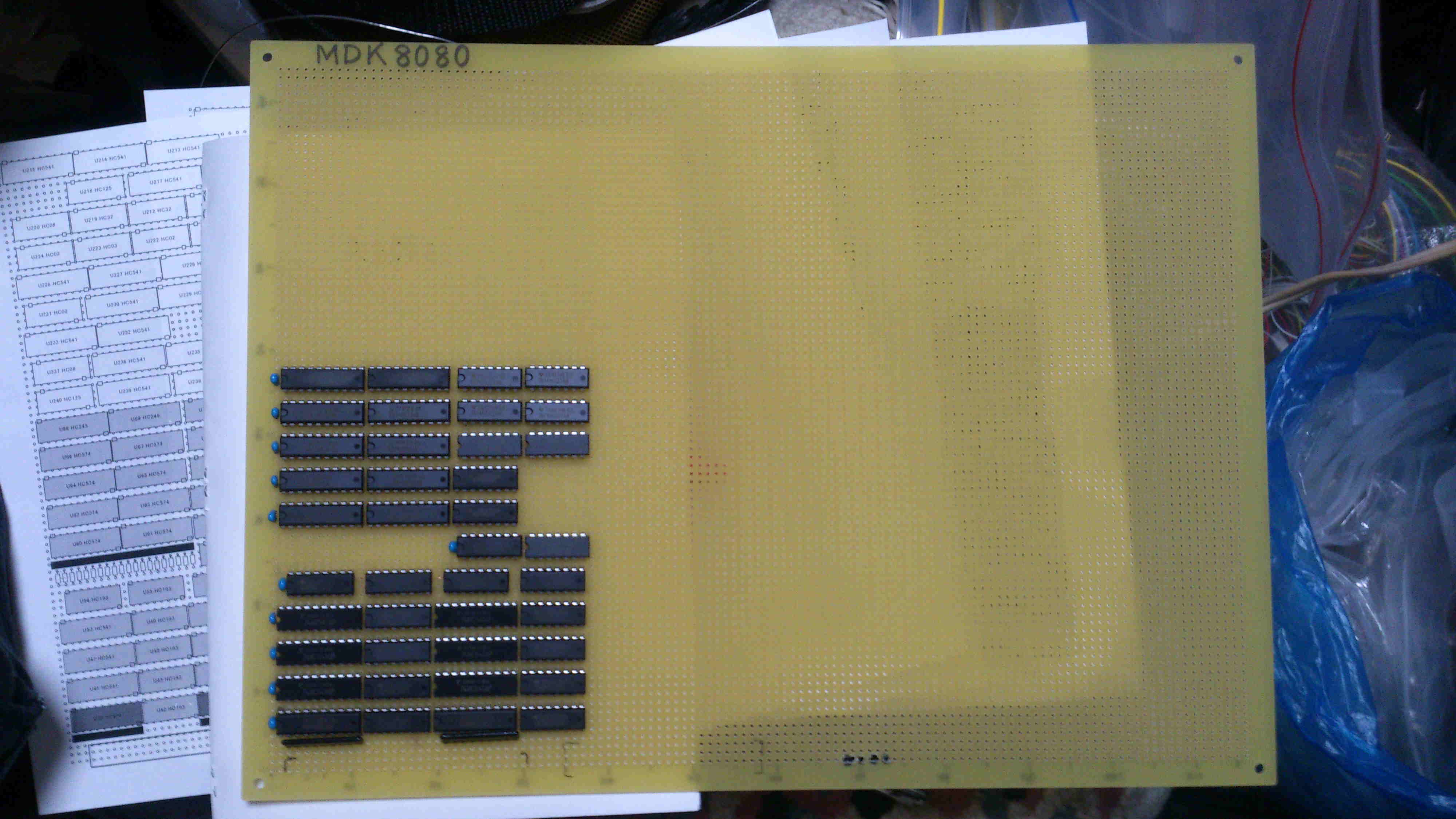

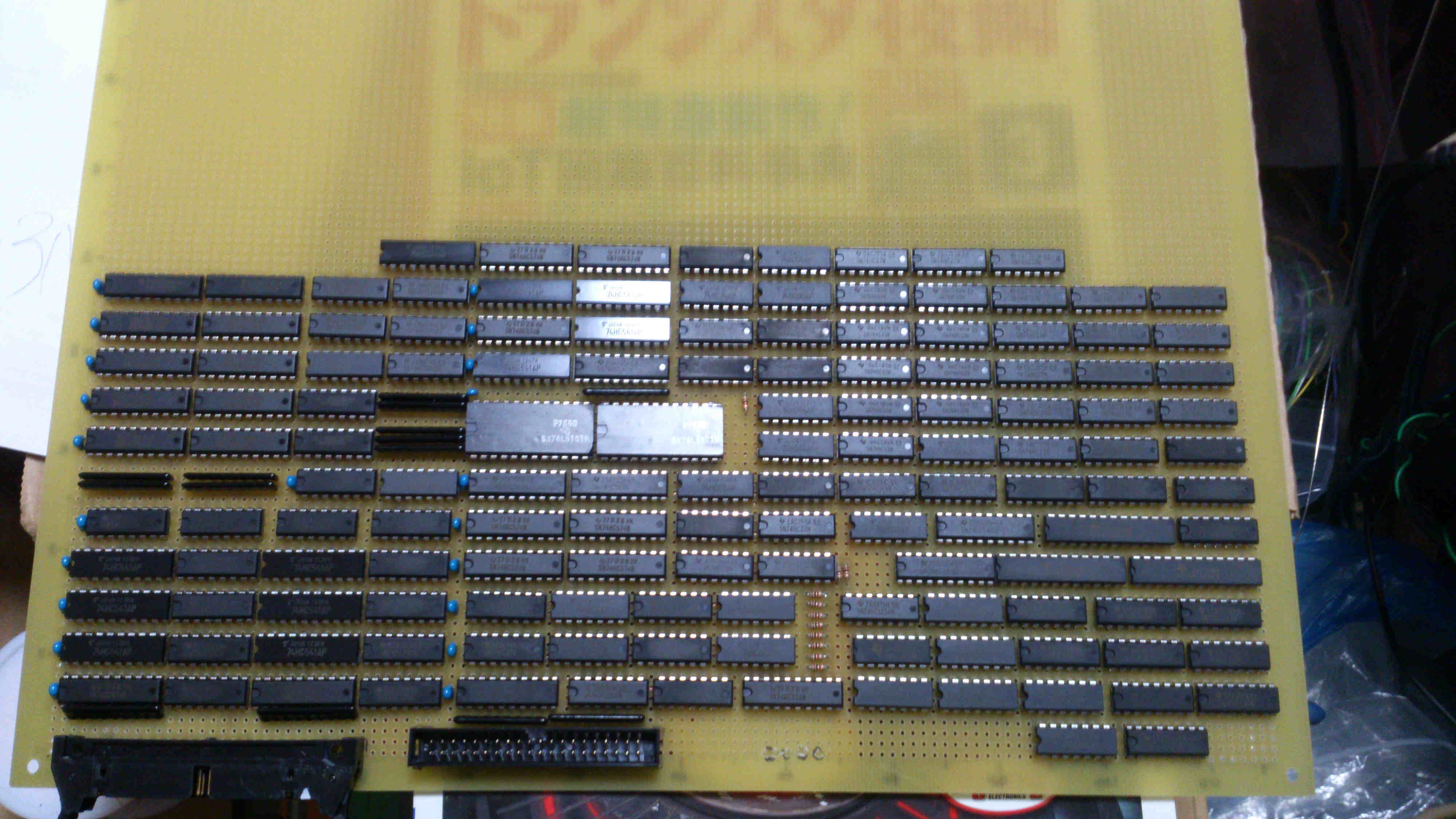

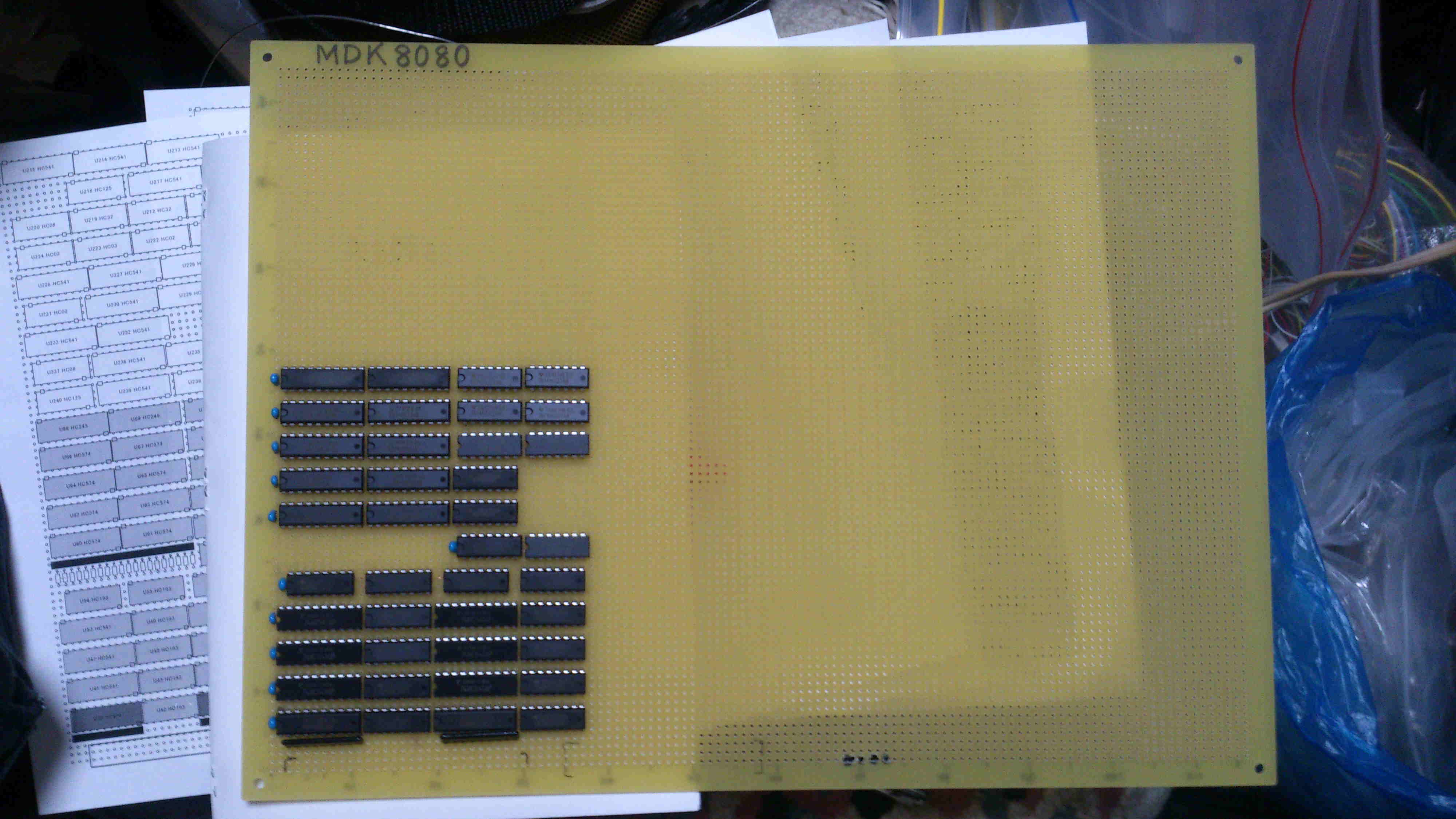

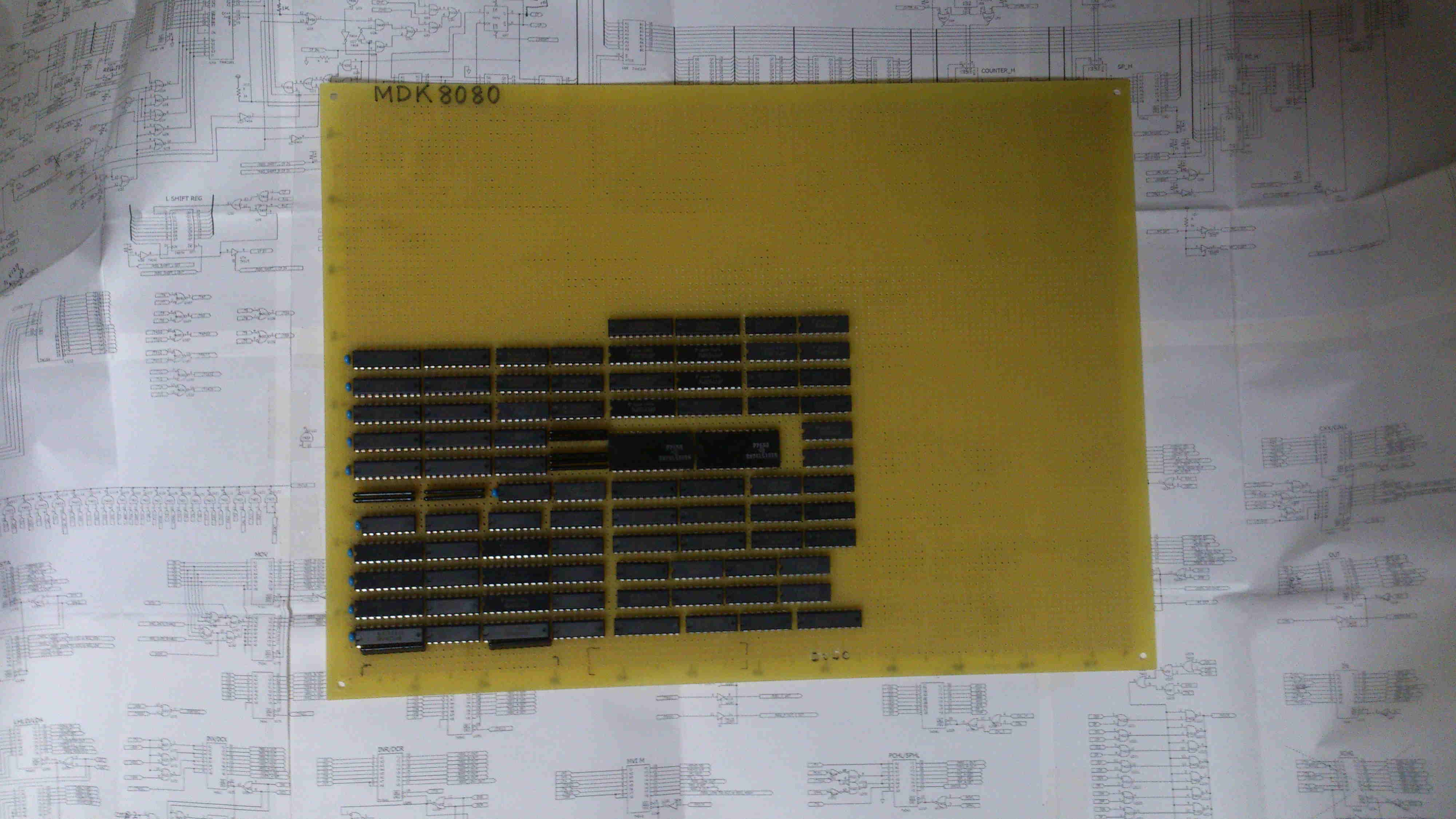

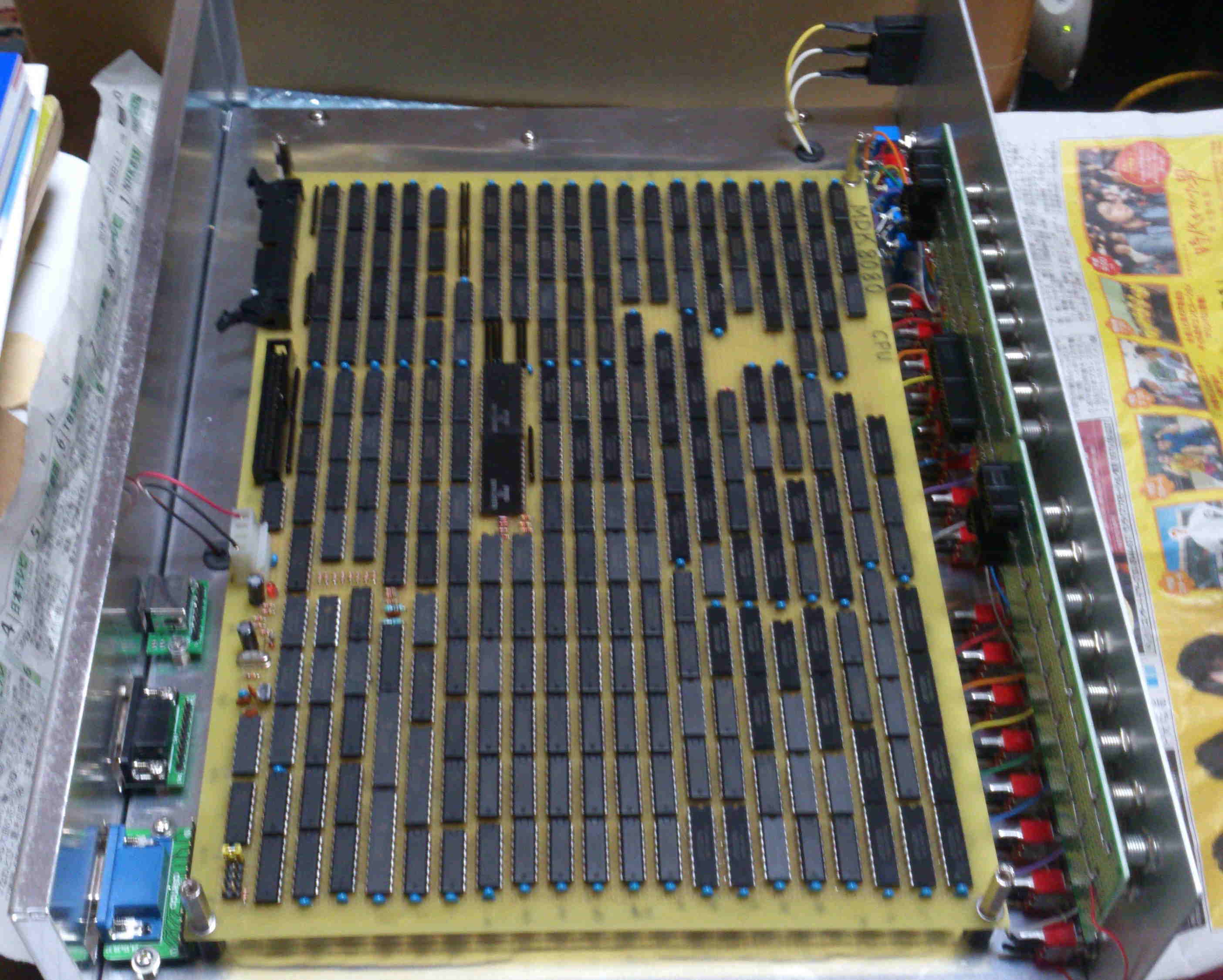

丂IC傪彮偟庢傝晅偗偰傒偨丅攝慄偼傑偩偙傟偐傜偱偁傞丅係侽杮乛擔偼偪傚偭偲恏偄側偁乮庛婥丒丒丒乯丅

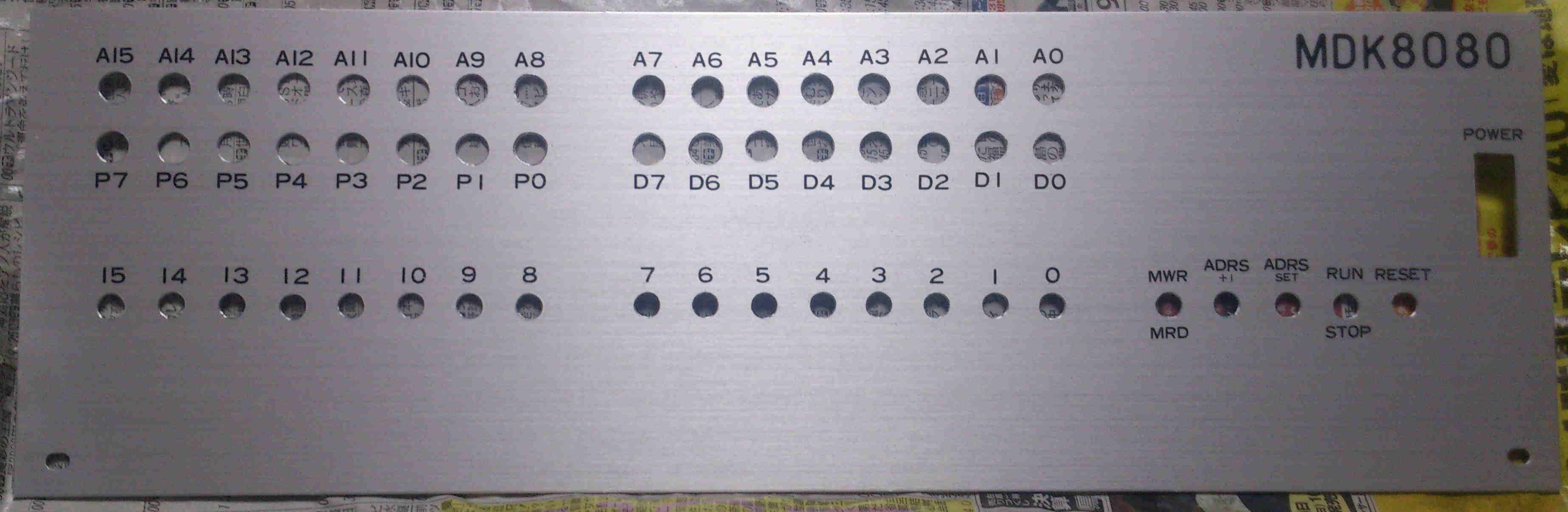

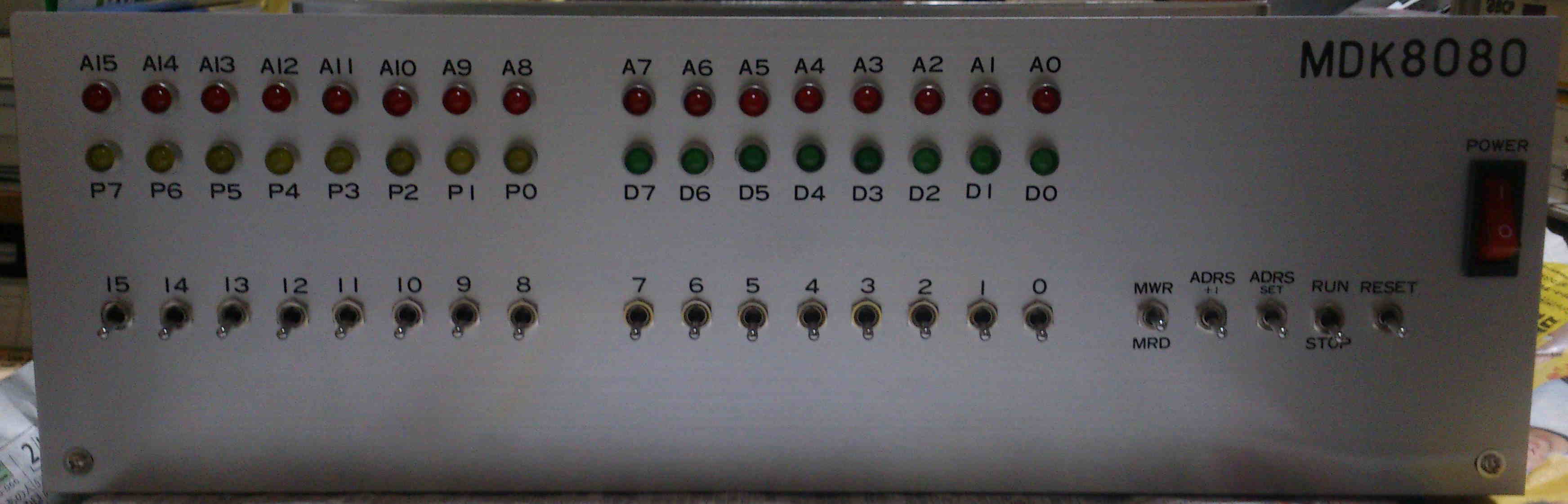

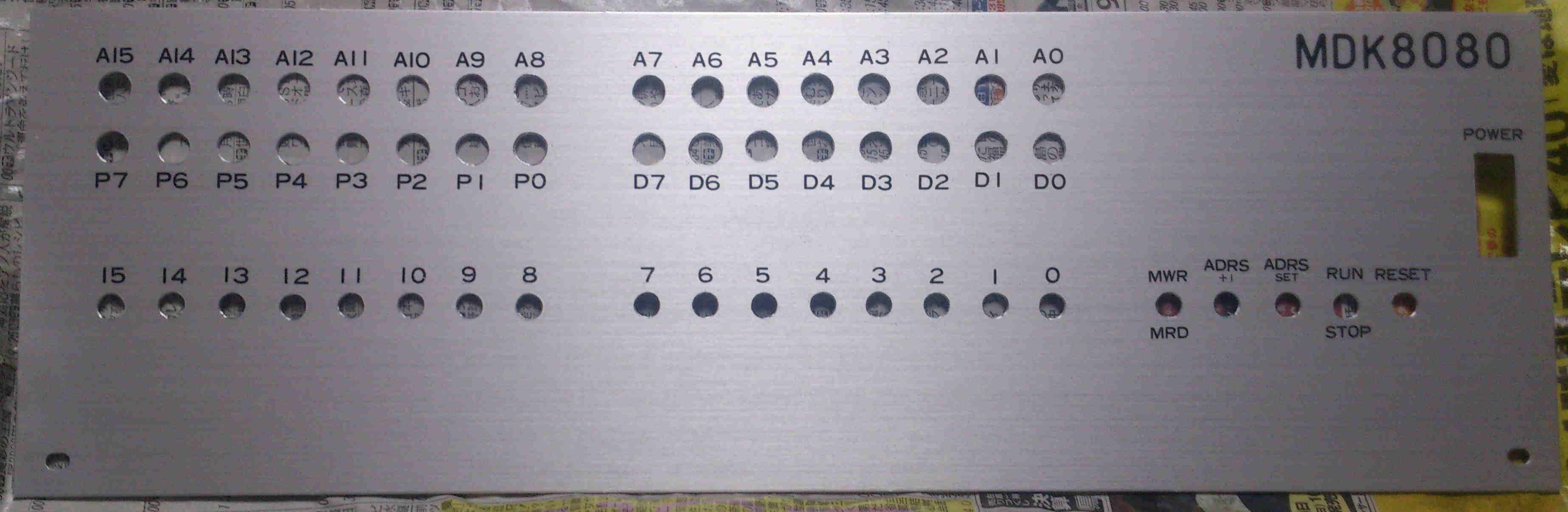

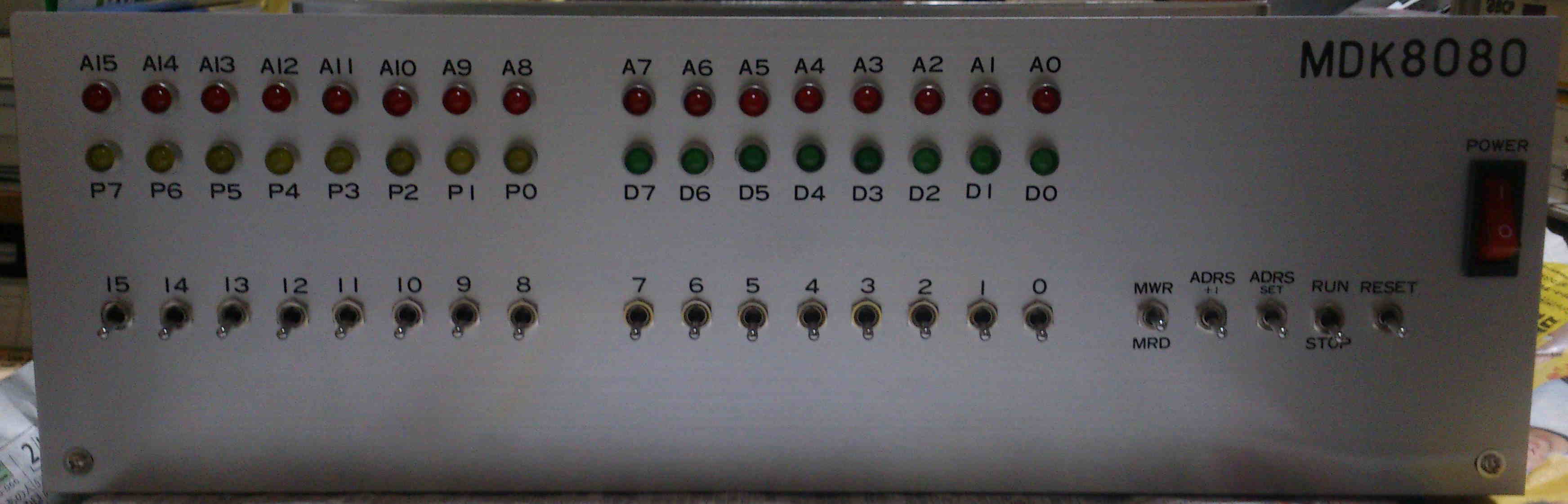

丂偦傟偲柤慜傪晅偗偰傒偨丅

丂MDK俉侽俉侽偲偟偨丅俉侽俉侽傕偳偒偱偁傞乮徫乯丅

俀侽侾俈擭俀寧

丂愭擔俬俠偑偦傠偭偨偲彂偄偨偑俈係俫俠侾俉侾偼傑偩撏偐側偄丅崱擔丄曉嬥梫媮傪偟偰偍偄偨丅

俙俴倀偼俈係俴俽侾俉侾傪巊偆偙偲偵偡傞丅俴俽傪俫俠偱庴偗傞偵偼僾儖傾僢僾偑昁梫偩丅俫俠俿僞僀僾偩偲庴偗傞偙偲偑偱偒傞偑丄俫俠偟偐攦偭偰偄側偄丅

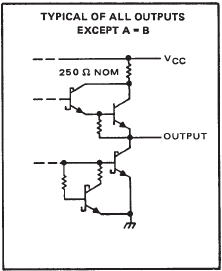

偪側傒偵俈係俴俽侾俉侾偺弌椡偼偙偺傛偆偵側偭偰偄傞丅偙傟偱偼偳偆婃挘偭偰傕俁丏俇倁埲忋偼弌偰偙側偄丅

俀侽侾俈擭俀寧

丂偡偙偟攝慄偟偰傒偨丅傑偩傑偩愭偼挿偄丒丒丒丒丅

俛倀俽埲奜偺攝慄敿偽丄偆乕傫丄係侽杮乛擔偼傗偭傁傝尩偟偄側偀丒丒丒丅姰惉偼墦偄偧偋丒丒丒丒丅傑偁丄偦傟偩偗挿偔妝偟傔傞偲偄偆偙偲偩偑乮偦偆巚偍偆乯丄懠偺偙偲偑弌棃側偄丅

巇曽側偄偗偳丅

俀侽侾俈擭俀寧

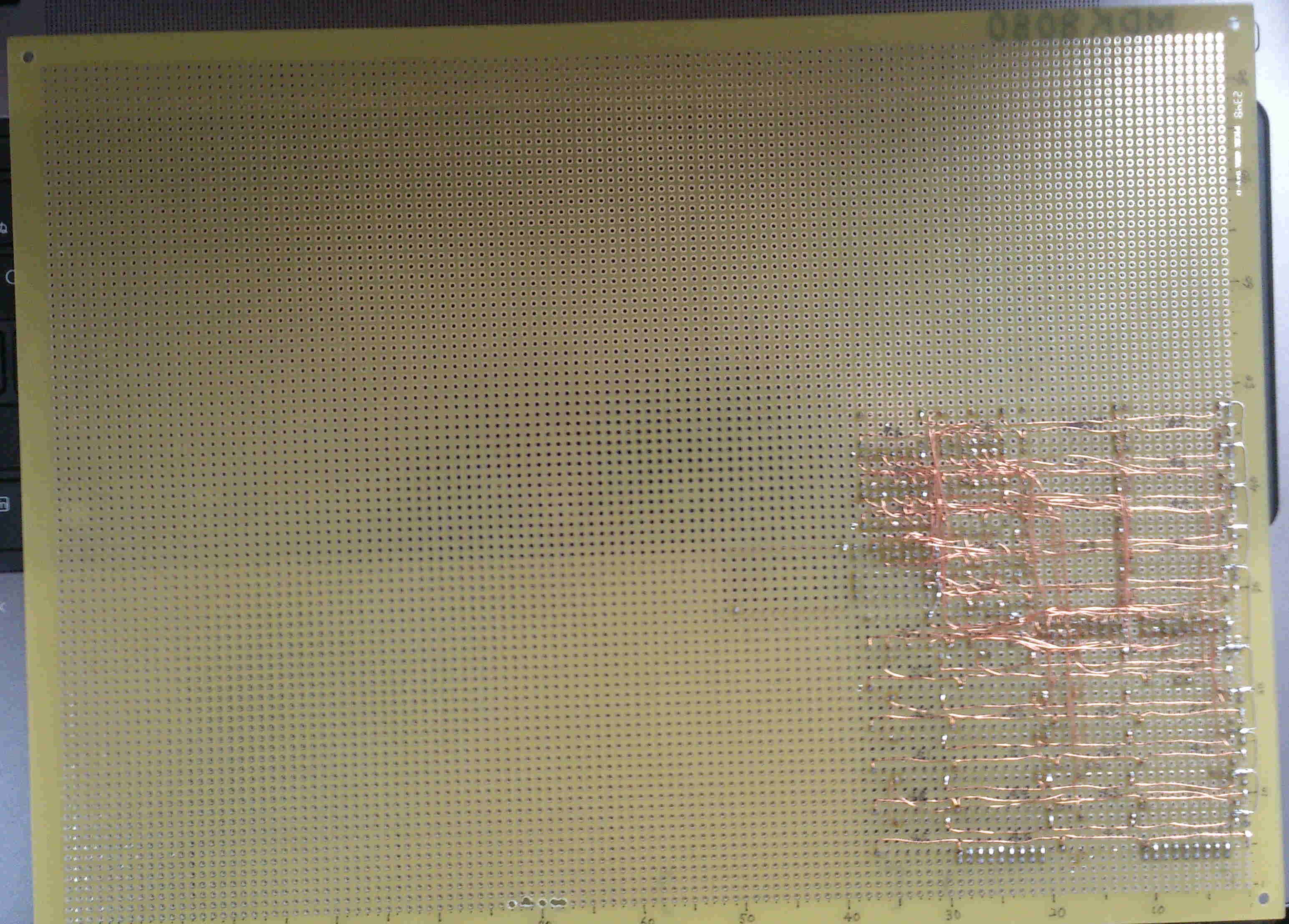

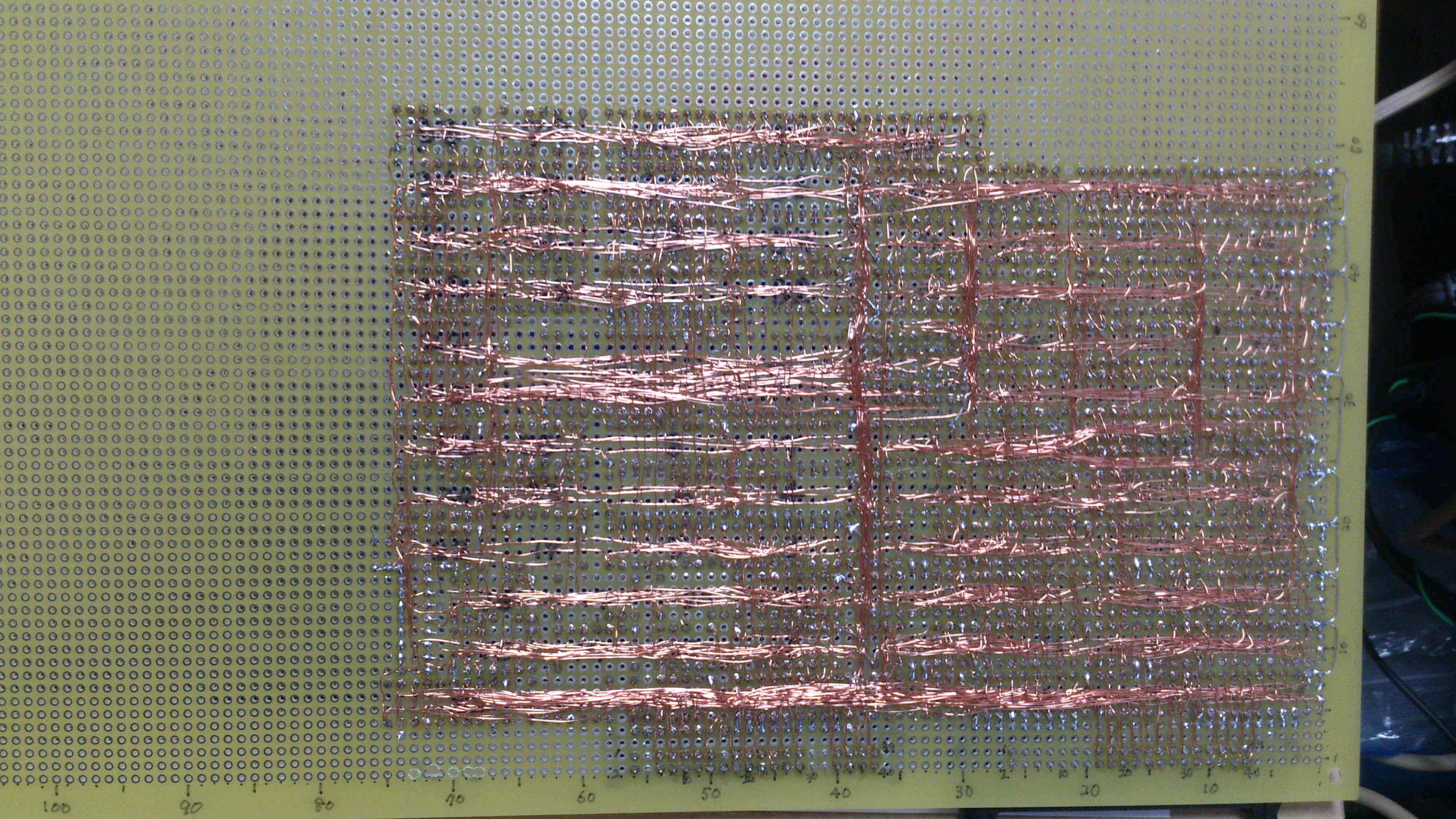

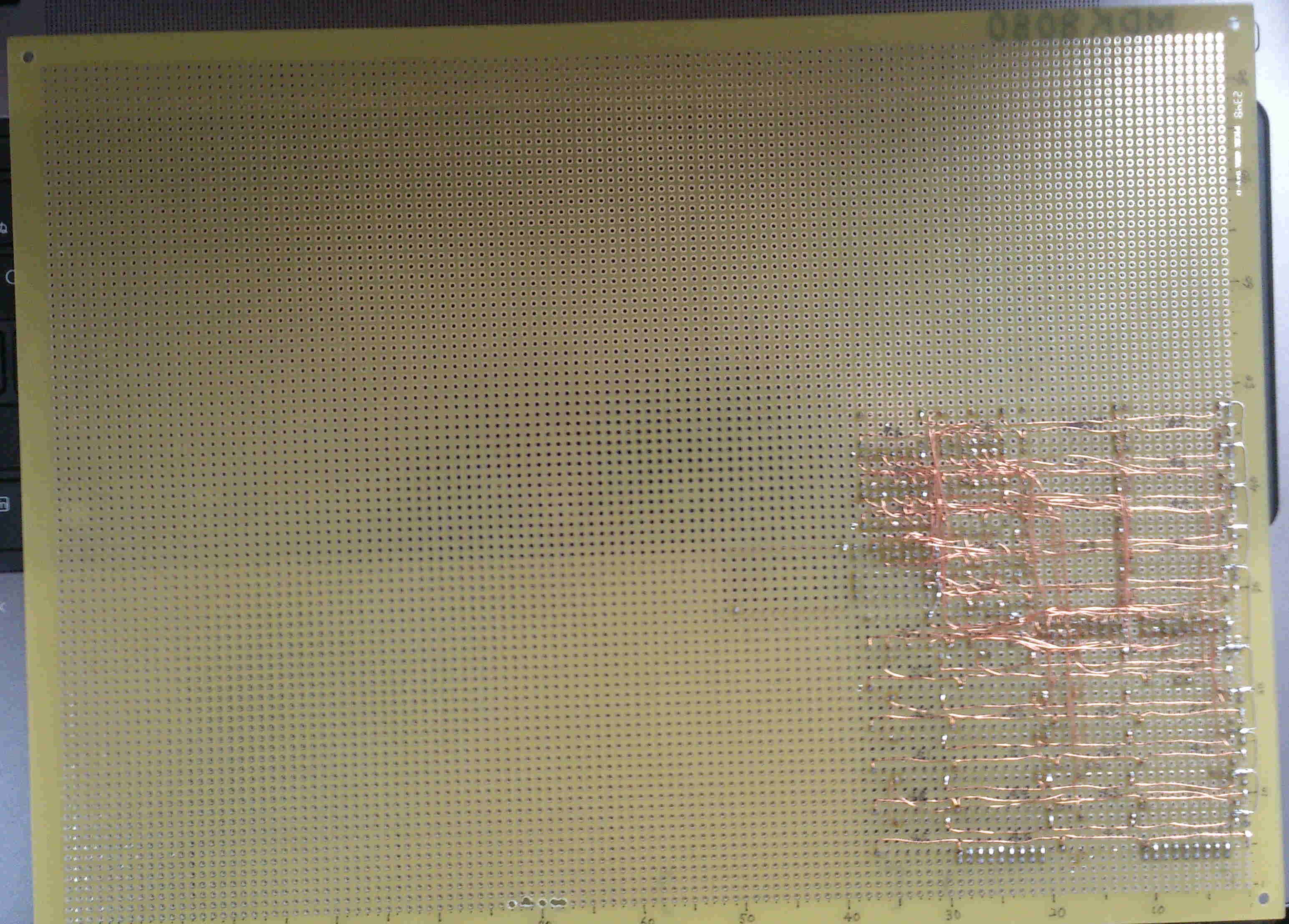

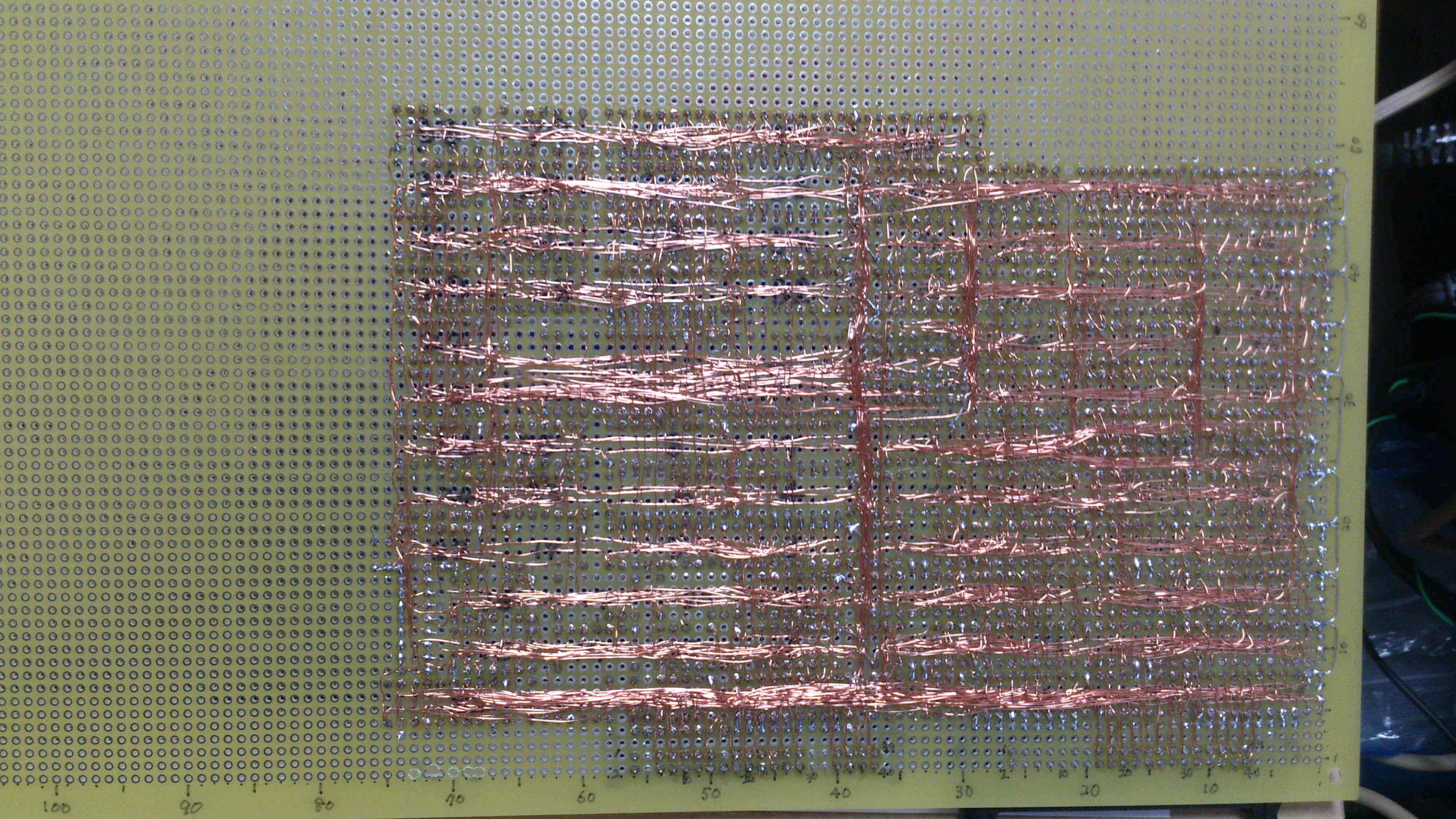

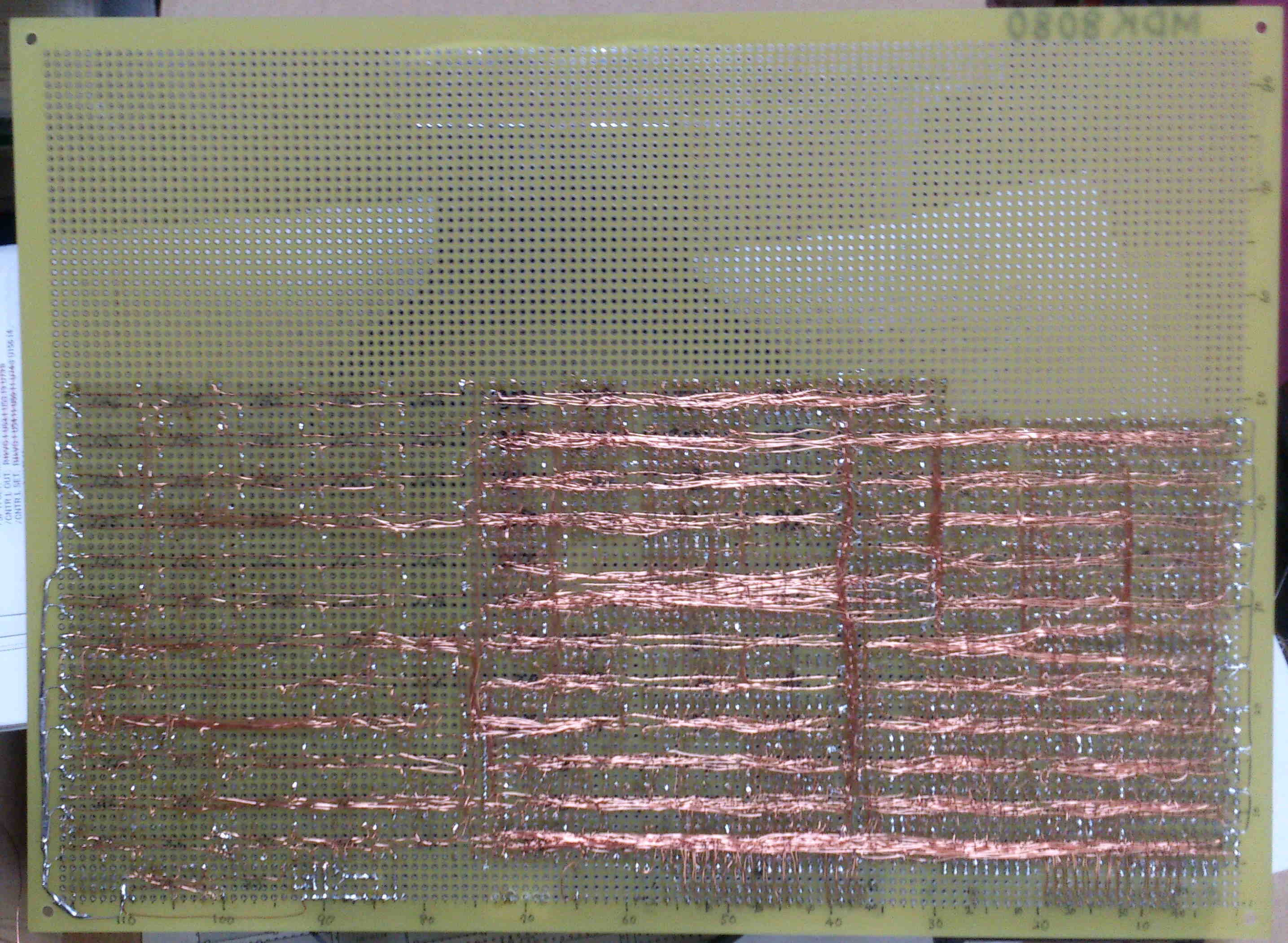

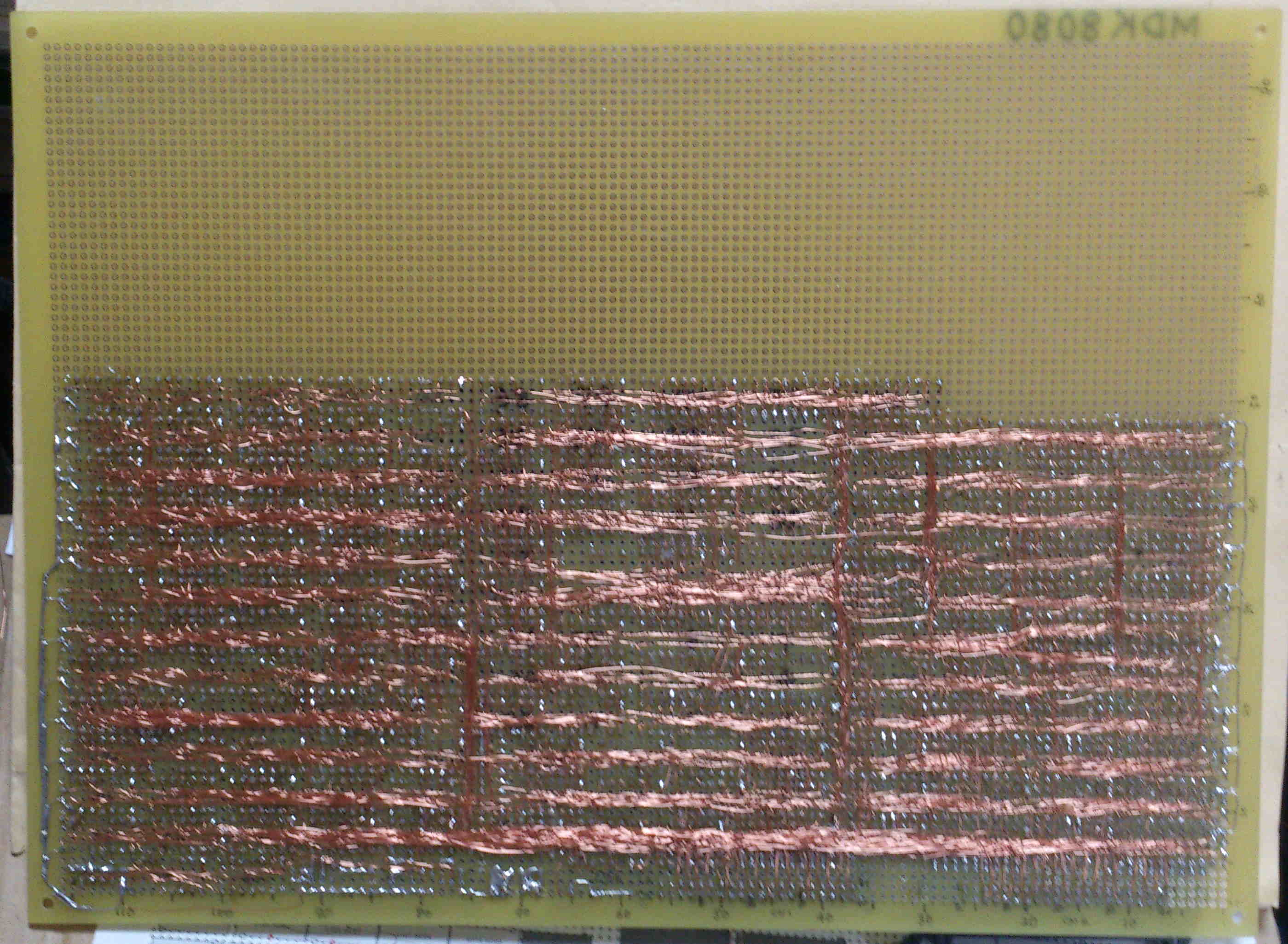

丂傛偆傗偔BUS偺攝慄偑廔傢偭偨丅

ALU廃傝傪幚憰偟偨丅

俀侽侾俈擭俀寧枛擔

丂俈係HC侾俉侾偺曉嬥庤懕偒偑姰椆偟偰丄曉嬥偝傟偨偙偲傪妋擣偟偨丅乮傗傟傗傟乯丅

側偺偱ALU偼俈係LS侾俉侾偱偁傞丅偰偐丄傕偆幚憰偟偰偁傞偑丅

俀侽侾俈擭俁寧拞

丂傛偆傗偔俙俴倀夞傝偺攝慄偑傎傏姰椆偟偨丅

俀侽侾俈擭俁寧拞

丂僋儘僢僋偲柦椷僨僐乕僟晹傪幚憰偟偨乮攝慄偼偙傟偐傜乯丅

俀侽侾俈擭俁寧拞

丂婏偟偔傕僞僀儉儕乕偵乮丠乯偙傫側杮偑敪攧偝傟偨丅偝偭偦偔峸擖偟偰傒偨丅弌斉幮偐傜捈愙攦偊傞偺偱峸擖偟偨丅捈愙峸擖偡傞偲僆儅働偺俠俢偑晅偄偰偄偰杮偺俹俢俥傗僜僼僩偺僜乕僗僼傽僀儖偑擖偭偰偄傞丅偙傟偼偍慐傔偩丅

乽僀儞僥儖俉侽俉侽揱愢乿偺杮丅岝偺嬶崌偑埆偔敀偭傐偔側偭偰偟傑偭偨丅

俀侽侾俈擭俁寧枛

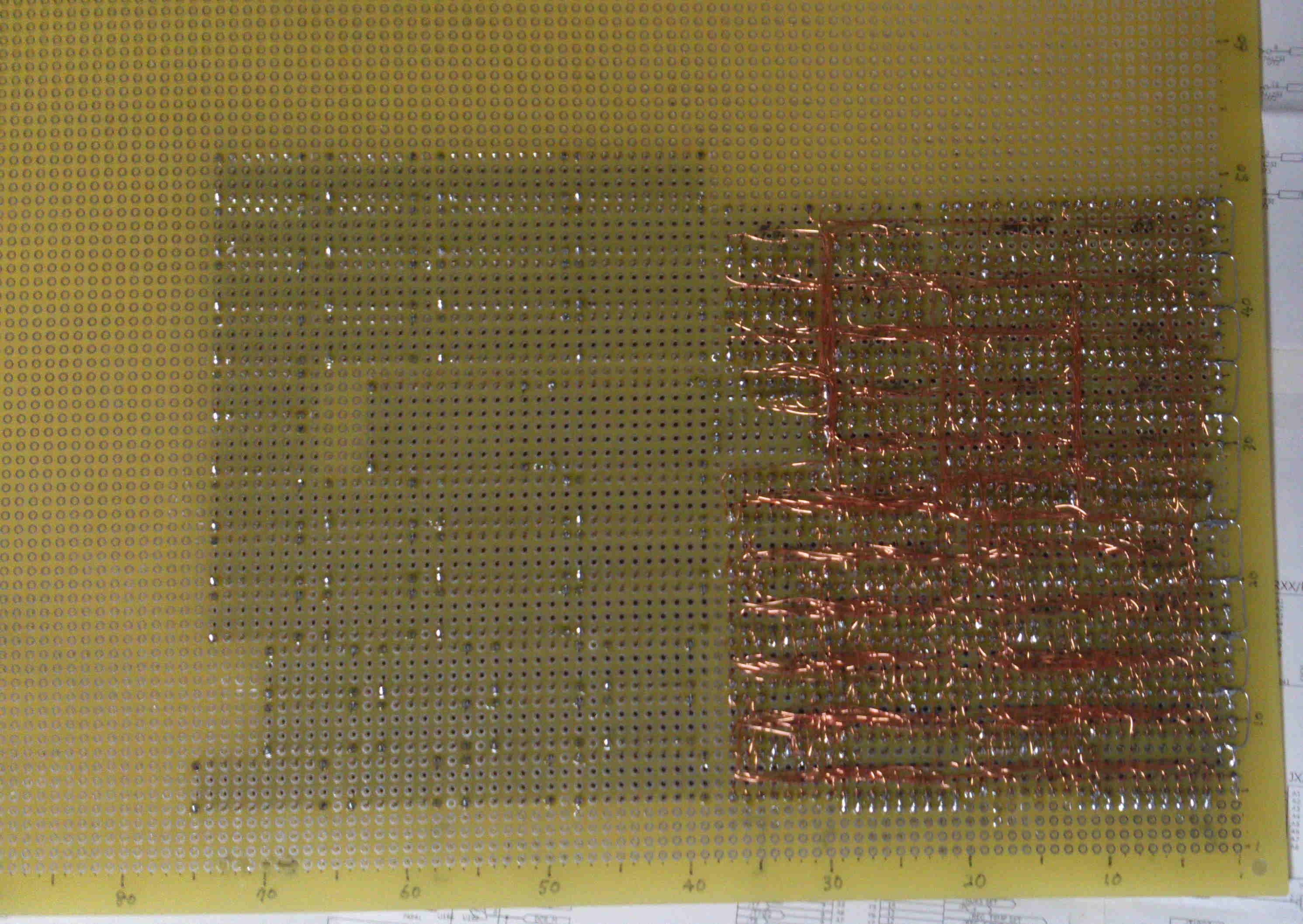

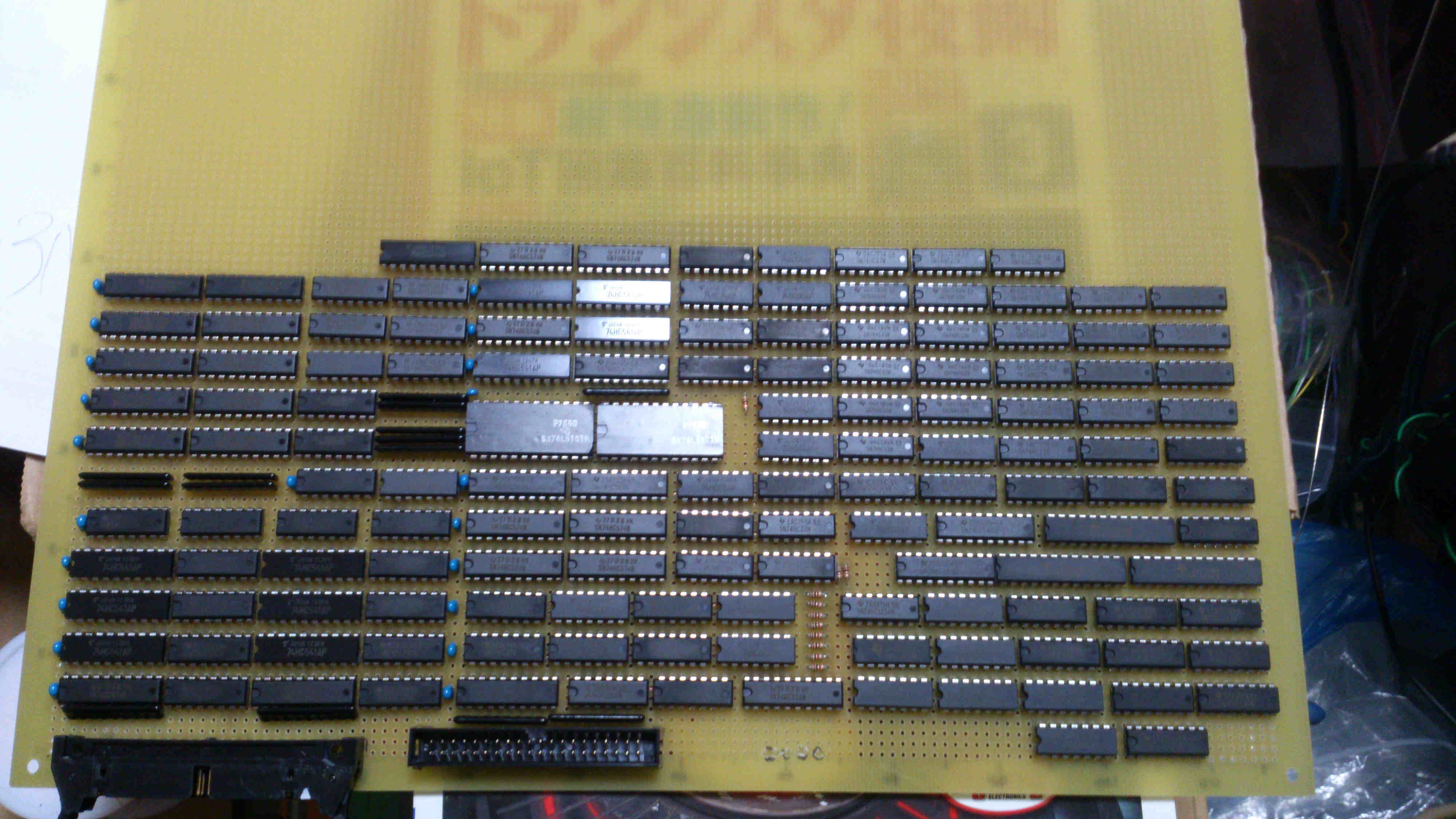

丂偩偄傇攝慄偑偱偒偰偒偨偑丄傑偩傑偩偩丅

偟偐偟丄偙偙傑偱攝慄偟偰俬俠偺僟僽傝偑敾柧偟偨丅偆乕乕乕傫傫丅偙偺俬俠偑柍偄偲俫俷俴俢傪庴偗晅偗側偄丅傛偟丄俫俷俴俢柍偟偩両丅偁偭両丒丒丒懸偰傛丅俫俷俴俢偑偱偒側偄偲俢俤俛倀俧夞楬偑巊偊側偄丅

巇曽側偄侾屄捛壛偩乮傗傟傗傟乯丅

崟偄儃僢僋僗僐僱僋僞偲敀偄僐僱僋僞偺娫偵侾屄捛壛偟偨丅

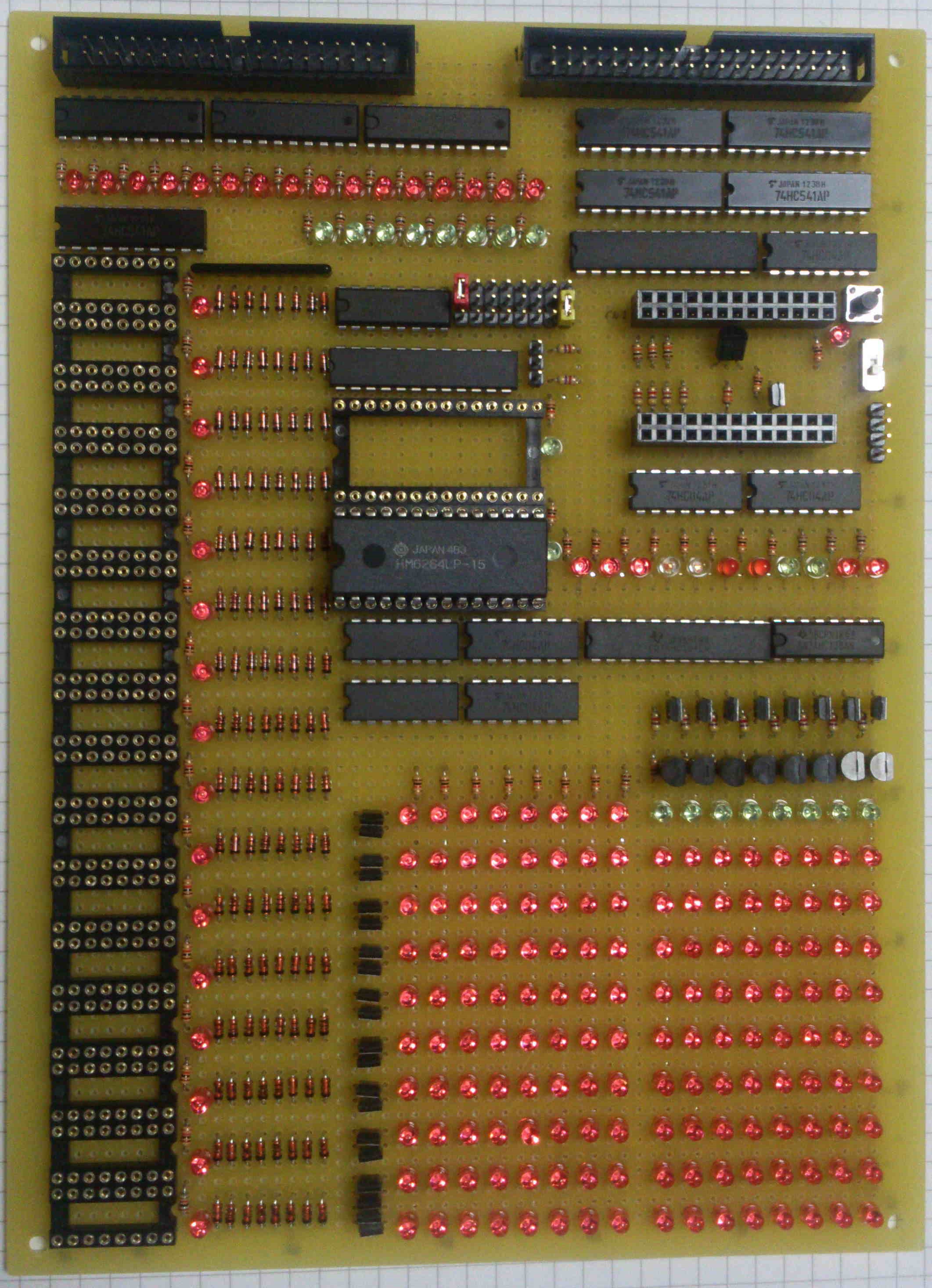

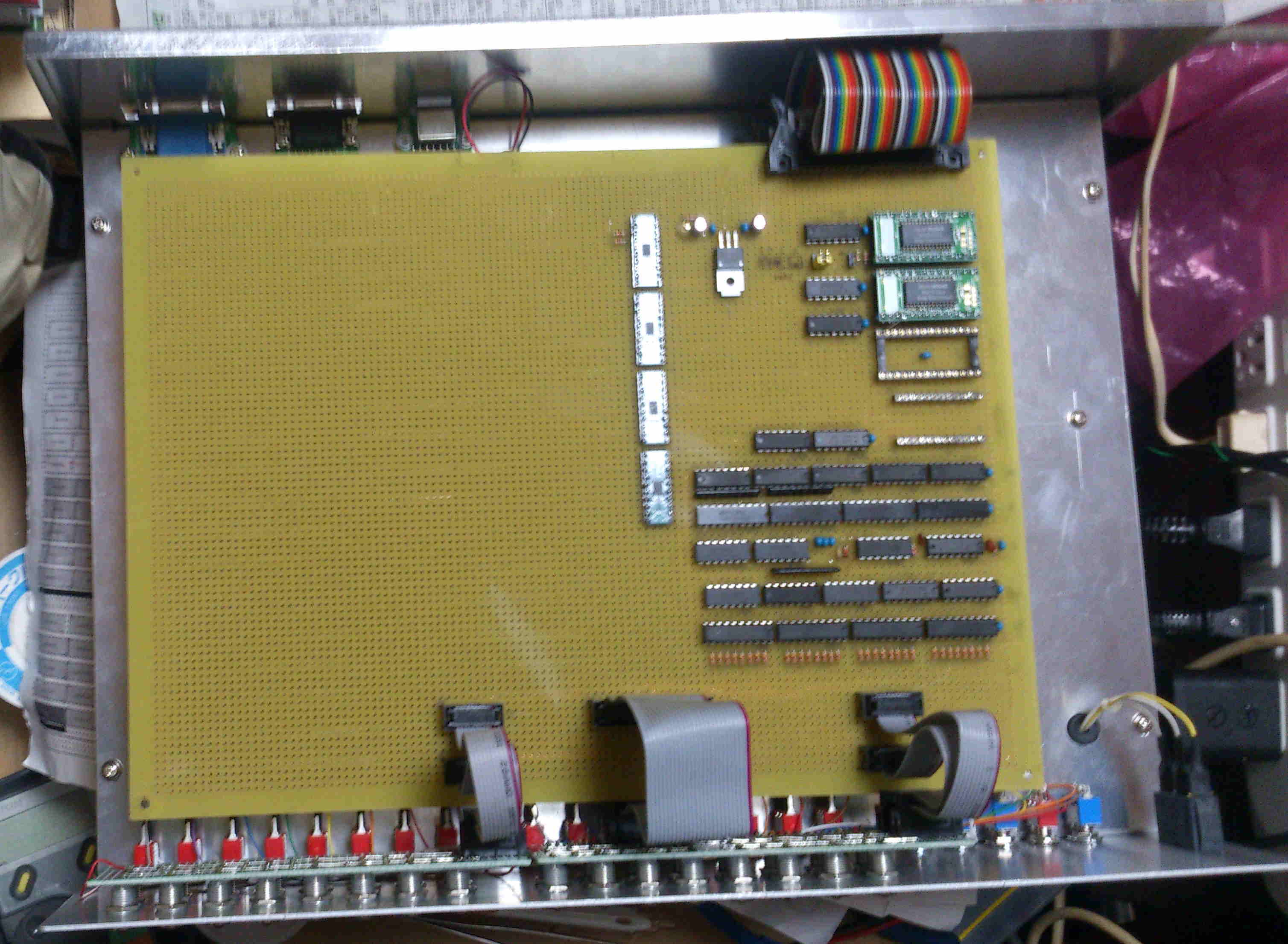

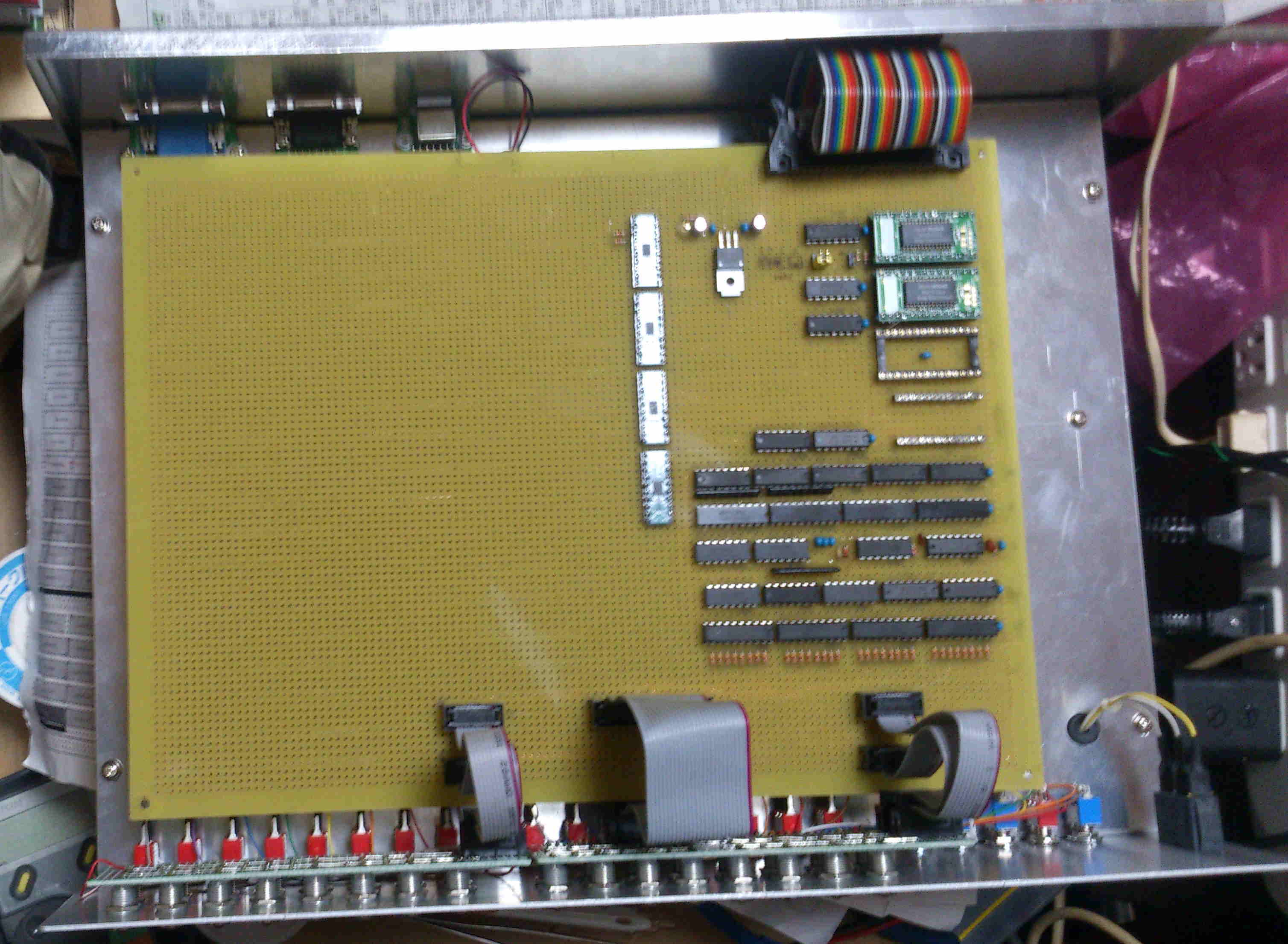

俀侽侾俈擭係寧拞

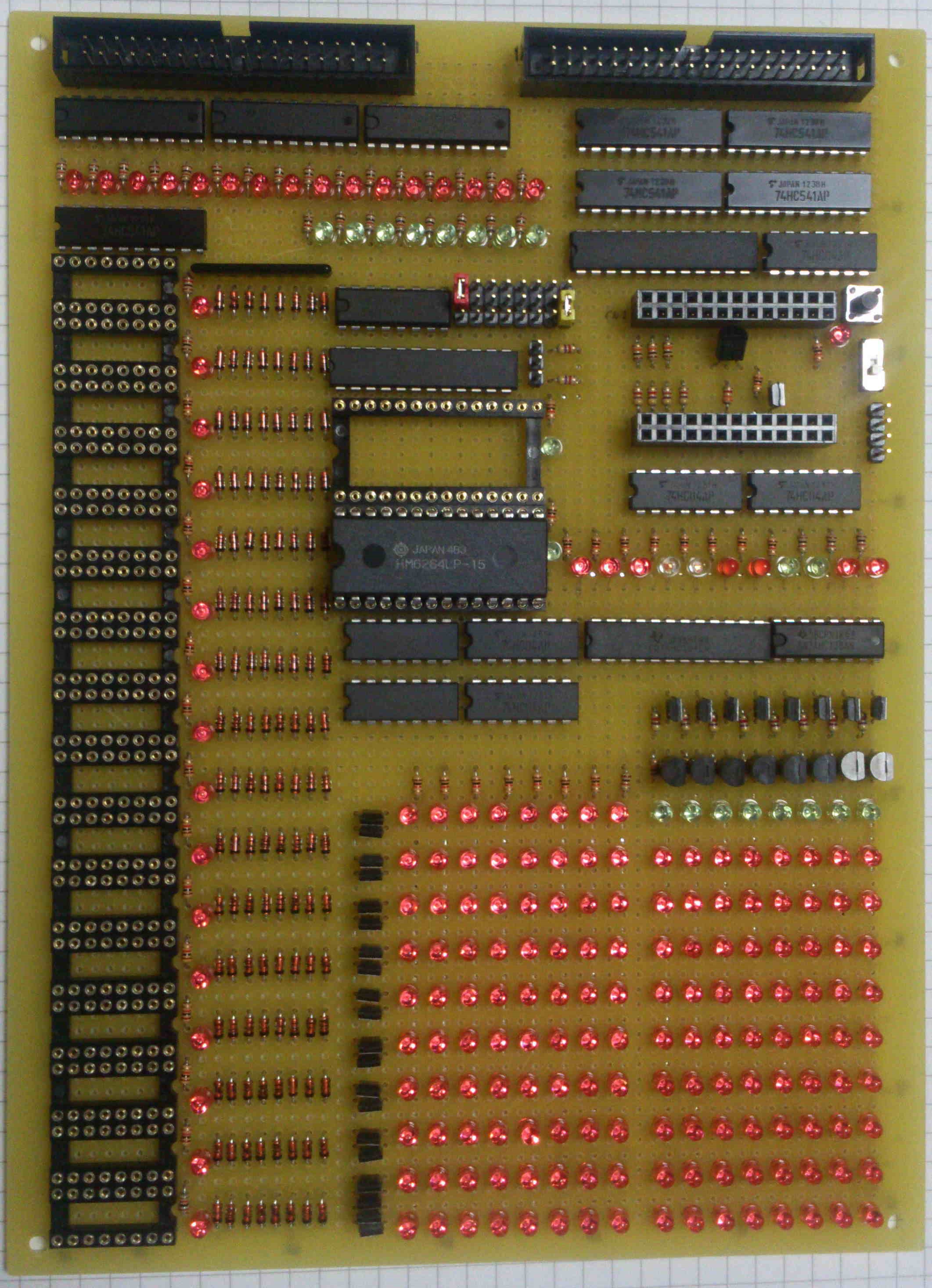

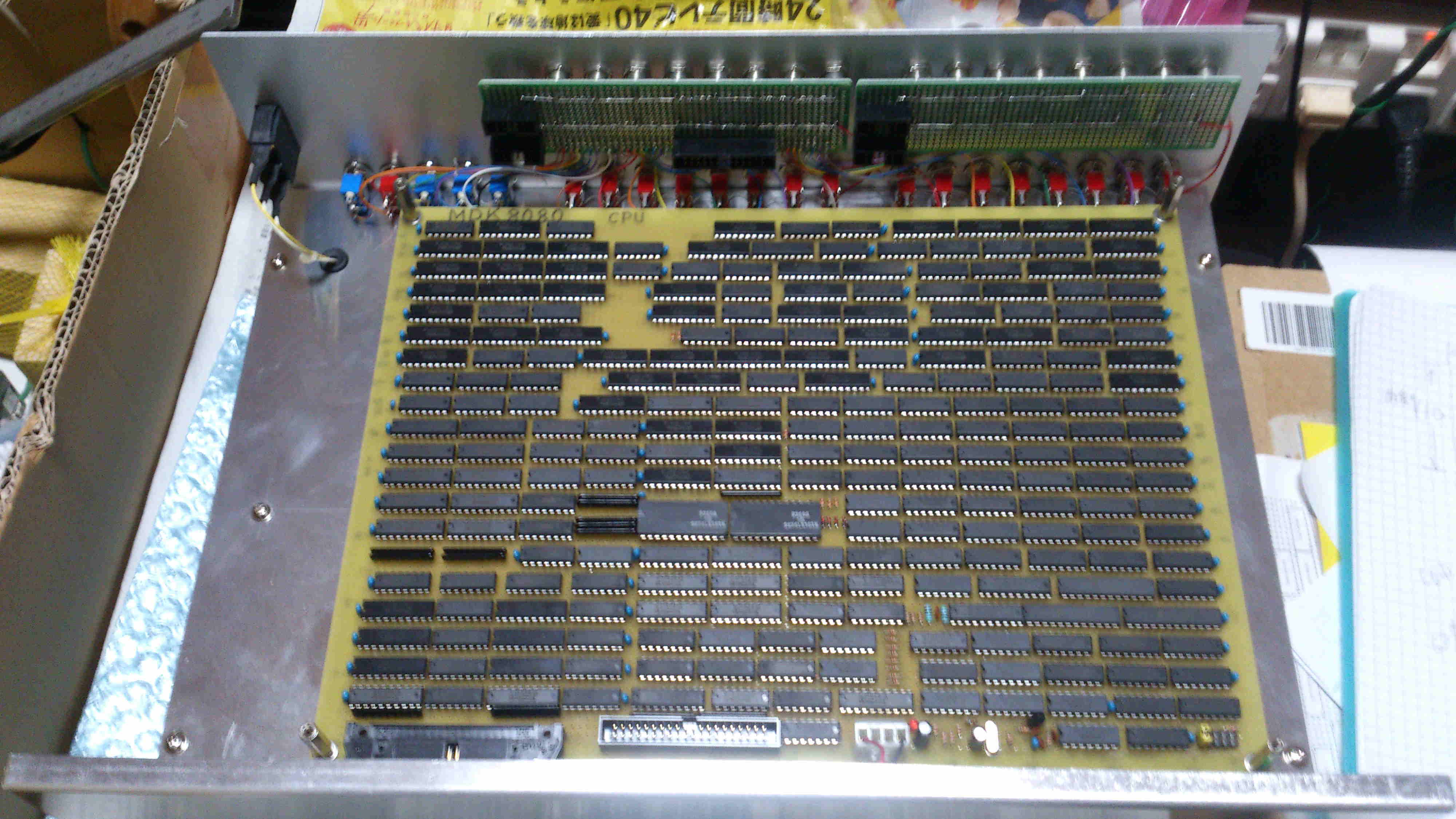

丂傛偆傗偔攝慄偑偱偒偨丅偲尵偭偰傕柦椷幚峴晹偼傑偩偩偑丅

丂偙偙傑偱弌棃傞偲柦椷僼僃僢僠偲僨僐乕僪偑摦嶌偡傞乮偼偢乯丅傑偁丄幚峴晹偑柍偄偺偱慡偰俶俷俹偩偑乮徫乯丅

偄傗丄幚峴晹偺晄梫側俶俷俹偼摦偔偼偢偩丄懠偵傕俽俿俠丆俠俵俠乮掶惓丗俠俵俠偼柦椷幚峴晹偑偁偭偨乯丄俫俙俴俿偑摦嶌偡傞偼偢偩偑丅

偦傟傪妋擣偡傞偨傔偺俢俤俛倀俧夞楬儃乕僪傪嶌傜偹偽丅

俀侽侾俈擭係寧枛

丂俢俤俛倀俧儃乕僪偱偁傞丅

傑偩姰惉偱偼柍偄丅晹昳傪晅偗偨偩偗偱偁傞丅僾儕儞僩婎斅側傜姰惉偩偑丒丒丒丅棤偺攝慄偼偙傟偐傜偱偁傞丅

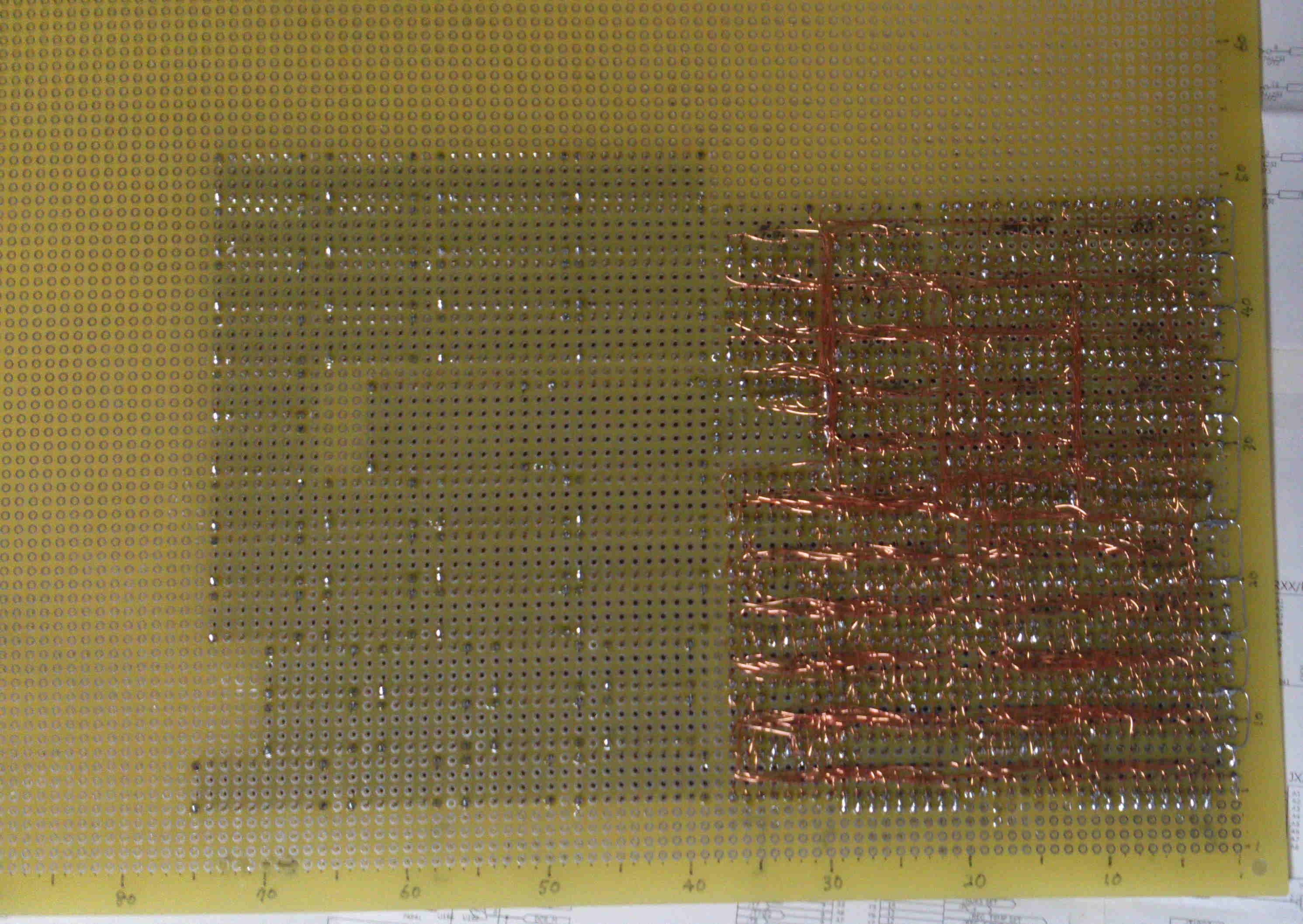

俵俢俲俉侽俉侽偺曽偼柦椷幚峴晹偑柍偄偺偱丄偍傛偦敿暘偺俬俠偟偐搵嵹偟偰偄側偄丅傕偆捈偖俧倂偩偑摉弶偺梊掕偺敿暘偟偐俬俠偑晅偄偰偄側偄偺偱丄係侽杮乛擔偼傗偭傁傝柍棟偩偭偨丅敿暘偺俀侽杮乛擔偭偰偲偙傠偩丅

俧倂偵俢俤俛倀俧夞楬偑姰惉偡傟偽屼偺帤偩丅偦傟偐傜俢俤俛倀俧偟側偑傜柦椷幚峴晹傪嵹偣偰偄偔偲丄杶媥傒慜偵姰惉偐側丅傑偁偦傫側偲偙傠偩傠偆丅

俀侽侾俈擭俆寧拞

丂俧倂偱偼俢俤俛倀俧夞楬偺攝慄偼廔傢傜側偐偭偨丅側偐偽偵傛偆傗偔姰惉偟偨丅偱偼俢俤俛倀俧夞楬偺俢俤俛倀俧偡傞夞楬傪丒丒丒丒丒側栿偵偼偄偐側偄丅

庢傝姼偊偢俠俹倀儃乕僪偵愙懕偟偰尒偨丅

塃抂偺俴俤俢孮偼儗僕僗僞傪撉傒弌偟偰昞帵偡傞丅撉傒弌偡偺偼俫俉儅僀僐儞偩丅俠俹倀偵俫俷俴俢傪妡偗偰摦嶌傪掆巭偟丄俢俤俛倀俧梡偺億乕僩偐傜儗僕僗僞偺撪梕傪撉傒弌偡巇妡偗偩丅

崱昞帵偟偰偄傞偺偼撉傒弌偟偨偮傕傝偺揔摉側抣偩丅幚嵺偵偆傑偔撉傒弌偡偐偼偙傟偐傜偱偁傞丅

俀侽侾俈擭俆寧枛

丂俫俉僜僼僩偺僶僌偑彮偟偁偭偨偑丄俢俤俛倀俧夞楬傕壗偲偐摦嶌偡傞傛偆偵側偭偨丅俢俤俛倀俧夞楬偑摦嶌偡傞傛偆偵側偭偰丄俠俹倀夞楬偺僴儞僟晄椙偑俆僇強偁傞偺傪敪尒偟偨丅

僴儞僟晄椙傪扱偔傋偒偐丄俢俤俛倀俧夞楬偑偆傑偔摦嶌偟偨偺傪婌傇傋偒偐丒丒丒丒丅

愭偵傕彂偄偨偑丄柦椷幚峴晹偺俬俠偑柍偔偰傕幚峴偱偒傞柦椷偺摦嶌妋擣傪偟偨丅

傑偢俶俷俹柦椷丅傑偁丄慡偰乮忋婰柦椷埲奜乯摦嶌偼俶俷俹偩偑丅摦嶌偡傞乮摉偨傝慜丠丠乯丅偍偦傜偔夞楬偵娫堘偄偑偁偭偰傕師傊恑傓偺偱傛偔傢偐傜傫偑丅

師偵俽俿俠偩丅俽俿俠傕偆傑偔摦嶌偟偨丅師偼俤俬偩丅俬俶俿丂俤俶俙俛俴俤傪僙僢僩偡傞偩偗側偺偱丄娙扨偵摦嶌偟偨丅師偼俢俬偩丅偝偭偒偺俤俶俙俛俴俤傪棊偲偡偩偗丅偙傟傕偆傑偔摦嶌偟偨丅

偝偰巆傞偼俫俙俴俿偩丅俫俙俴俿柦椷偱幚峴偑掆巭偟偨丅掆巭偟偨偲尵偭偰傕俬俶俿丂俤俶俙俛俴俤偵偟偰偄傞偲俬俶俿俤俼俼倀俹俿傪庴偗晅偗側偗傟偽側傜側偄丅偲傝偁偊偢岻偔偄偭偨丅偨偩偟柦椷幚峴晹偑側偄偺偱俼俽俿柦椷偑幚峴偱偒側偄丅俶俷俹偲側偭偰師傊恑傓丅崱偺抜奒偱偼俷俲偩丅

偙偙傑偱偆傑偔摦嶌偟偨偺偱丄婥傪傛偔偟偰柦椷幚峴晹傪幚憰偡傞丅

俀侽侾俈擭俇寧弶

丂俴倃俬柦椷偲俢俙俢柦椷偑幚憰偱偒偨丅憗懍僥僗僩偟偰傒傞丅

丂俴倃俬丂俛丄係係俆俆俫

丂俴倃俬丂俢丄俉俉俙俙俫

丂俴倃俬丂俫丄侽俠俠俁俁俫

丂俴倃俬丂俽俹丄侽俥侽侽俥俫

丂偲僷僞乕儞偑僟僽傜側偄傛偆偵僨乕僞傪擖傟傞丅

儗僕僗僞偺撪梕偼撉傒弌偟偰俴俤俢傪揰摂偝偣偰偄傞丅偆傓偆傓丄偆傑偔偄偭偨偧丅

俢俬俹俽倂偺堦斣壓偼俫俙俴俿柦椷偩丅撍偭憱傜側偄傛偆偵俫俙俴俿柦椷傪抲偄偰偄傞丅

偝偰丄俢俙俢柦椷偺僥僗僩偩丅俴倃俬柦椷偑柍偄偲儗僕僗僞偵僨乕僞愝掕偑偱偒側偄偺偱丄俴倃俬偑摦嶌偟偰偐傜偺僥僗僩偩丅

丂俢俙俢丂俛

丂俢俙俢丂俢

丂俢俙俢丂俫

丂俢俙俢丂俽俹

傪帋偟偰傒傞丅偙傟偼俙俴倀傪巊偭偰丄俴儗僕僗僞偼俙俢俢柦椷丄俫儗僕僗僞偵偼俙俢俠柦椷偱偦傟偧傟偺儗僕僗僞傪懌偟崬傓丅

傑偢偼偆傑偔寘忋偑傝偡傞偐偳偆偐丅

丂俴倃俬丂俫丄侽侽侽侽侾俫

丂俴倃俬丂俛丄侽俥俥俥俥俫

丂俢俙俢丂俛

傪幚峴丅寘忋偑傝偟偰俫俴儗僕僗僞偼侽偲側傝俠僼儔僌偼俷俶偟偰偄傞丅俢俙俢柦椷偱曄壔偡傞偺偼俠偩偗偩偑丄僥僗僩偺堊慡偰偺僼儔僌傪僙僢僩偟偰偄傞丅

俙俠偑俷俶丄倅偑俷俶偟偰偄傞丅偍傗乣丄俽傕俷俶偟偰偄傞丅侽偩偐傜倅偑俷俶偟偰惓夝偩偑丄俽偑俷俶偡傞偺偼偍偐偟偄丠丠

夞楬恾傪挷傋偨傜丄壗偲両娫堘偭偰偄傞丅晧榑棟偵偟偨偲偒偵丄曄偊側偗傟偽側傜側偄傪偦偺傑傑偵偟偰偄傞丅傗傟傗傟丅

愙懕傪曄峏偩丅攝慄傪捛偭偐偗傛偆偲丄俽偺儔僢僠俬俠傪尒傞偲丅側丄偭側丄側傫偲丄攝慄偑柍偄両両丅偄傗乣丄嵨偺偣偄偐側丅夞楬傪娫堘偭偰偄偨偆偊攝慄偟偰偄側偄偲偼両

儈僗偺儈僗偱儈僗偺俀忔偱偁傞乮偲傎傎乯丅偦偺偍偐偘偱乮丠乯攝慄曄峏偑妝偩乮側傫偰偹丒丒丒乯丅

攝慄傪捛壛偟偰丄摦嶌俷俲偲側偭偨丅偦偺屻丄俢俙俢柦椷偱俠僼儔僌偩偗曄壔偡傞傛偆偵攝慄傪曄偊偨丅

俀侽侾俈擭俇寧拞夁

丂俽俫俴俢丄俽俿俙柦椷偲俴俫俴俢丄俴俢俙柦椷偑偱偒偨丅偦傟偧傟偺柦椷偼娭楢偑偁傝傛偔帡偰偄傞偺偱夞楬偵嫟捠晹暘偑偁傞丅嫟梡晹暘偑偁傞偺偱丄偦傠偊偰嶌偭偨傎偆偑妝偩偭偨偺偩丅

偝偰丄摦嶌妋擣偩丅俽俿俤俹偱摦嶌偝偣傞偲偆傑偔摦嶌偟偨丅

偦偙偱楢懕摦嶌偱僥僗僩偡傞偨傔偺僾儘僌儔儉傪愝掕偟偨乮慻傫偩乯丅

俴倃俬丂俫丄侽俙俙俠俆俫

俽俫俴俢丂侽俥侽侽侽俫

俴俢俙丂侽俥侽侽侽俫

俽俿俙丂侽俥侽侽侾俫

俴俫俴俢丂侽俥侽侽侽俫

俫俙俴俿

偙偺寢壥

俙儗僕僗僞亖侽俠俆俫

俫俴儗僕僗僞亖侽俠俆俠俆俫

偲側傞偼偢偱偁傞丅

俽俿俤俹摦嶌偱偼偆傑偔偄偭偨偺偱丄僋儘僢僋侾俵俫倸偱幚峴偝偣偰傒偨丅寢壥偼忋乆丄儔僋僠儞儔僋僠儞丅

偱偼俀俵俫倸偱偼偳偆偩傠偆丅

丒丒丒丒丒偊偭両丂偆丄偆傑偔摦偐側偄丅俫俴儗僕僗僞偑侽俙俙俠俆俫偺傑傑偩丅偍傗乣丅

僋儘僢僋侾俵俫倸偺俠俹倀偭偰偙偲偋乣丅偄傗偄傗偦傫側偼偢偼丒丒丒丒丅

擸傫偱傕偟傛偆偑側偄丅儘僕僢僋傾僫儔僀僓偺弌斣偩両丅

偁傟傗傜偙傟傗傜挷傋偭偨寢壥丄傾僪儗僗偺俙侾係偺曄壔偑曄側偙偲偵婥晅偄偨丅

儘僕僢僋傾僫儔僀僓側偺偱丄攇宍偼嬮宍偱偁傞偑丄攇宍偺曄壔僞僀儈儞僌偐傜尦攇宍偑側傑偭偰偄傞偺偱偼側偄偐偲媈偭偨丅偙傟偽偭偐傝巊偭偰偄傞偲攇宍偺僞僀儈儞僌偐傜尦攇宍偑偍偐偟偄偺偱偼偲壗偲側偔暘偐傞傛偆偵側傞傕偺偱偁傞丅

憗懍俙侾係偺儔僀儞傪挷傋偰偄偔偲丒丒丒價儞僑両丅敿揷晄椙傪尒偮偗偨丅

庤捈偟偡傞偲俀俵俫倸偱傕摦嶌偟偨丅

敿揷晄椙側偺偵侾俵俫倸偱偼壗屘摦嶌偡傞偺偐丠乮悇應偩偑乯敿揷晄椙晹偼崅掞峈偱宷偑偭偰偄偰丄怣崋偼偁傞掱搙揱傢傞偺偱偼丅俠俵俷俽亅俬俠偼擖椡僀儞僺乕僟儞僗偑崅偄偺偱丄怣崋傪庴偗庢傟傞偺偩傠偆丅TTL偼揹棳偱摦嶌偡傞偺偱偦偆偼偄偐側偄偑丅僋儘僢僋偑憗偔側傞偲崅掞峈偲晜梀梕検偱僼傿儖僞偺傛偆偵側偭偨晹暘偱怣崋偑揱傢傝偵偔偔側傞偺偱偁傠偆丅

丂偝偰俀俵俫z偑摦嶌偟偨偺偱丄帋偟偵係俵俫z偵偟偰尒偨丅丒丒丒丒傗偭傁傝丒丒丒丒摦嶌偟側偄丅偦傫側傕傫偐側偀丄傑偁婜懸偼偟偰偄側偐偭偨偑丅儘僕僢僋傾僫儔僀僓偑宷偑偭偰偄傞偺偱丄攇宍傪嵦偭偰尒偨丅

偍傗偭両傾僪儗僗儔僢僠偑偆傑偔偄偭偰側偄晹暘偑偁傞丅偦偺晹暘埲奜偼偪傖傫偲儔僢僠偱偒偰偄傞丅丒丒丒丒丒丒偁偭丒丒丒丒丒媫偵巚偄弌偟偨丅敿擭慜偵夞楬愝寁帪偵摢傪傛偓偭偨偙偲偑丒丒丒丅

偍偐偟偔側偭偰偄傞偺偼俽俿俙柦椷偺屻偩丄俽俿俙柦椷偼俽俫俴俢柦椷傪敿暘偮偐偆丅俴儗僕僗僞傪儊儌儕乕偵彂偔偐傢傝偵俙儗僕僗僞傪彂偄偰丄儅僔儞僒僀僋儖傪儕僙僢僩偡傞丅儕僙僢僩偟側偗傟偽偦偺傑傑俫儗僕僗僞傪彂偄偰偟傑偆丅偙偺幚峴俬俠偺傾僪儗僗儔僢僠怣崋偑惗偒偰偄傞乮俫偺忬懺丄僩儔僀僗僥乕僩偑傾僋僥傿僽偵側偭偰偄傞乯丅偙傟偲俽俿俙柦椷偺師偺柦椷傪僼僃僢僠偡傞偨傔偺俹俠傪儔僢僠偡傞怣崋夞楬偑働儞僇偟偰偄傞丅偠傖偁壗屘俀俵俫倸偱偼摦嶌偡傞偺偐丠丠偙傟偼傛偔傢偐傜傫丅

柦椷傪僼僃僢僠偟偰偟傑偊偽丄俽俿俙柦椷幚峴怣崋偑愗傝懼傢傞偺偱偁傞偑丄僼僃僢僠偱偒側偗傟偽愗傝懼傢傜側偄丅幚嵺偵偼嫮惂揑偵僼僃僢僠摦嶌偡傞偺偱丄偳偙偩偐暘偐傜側偄乮傾僪儗僗儔僢僠偵幐攕偟偰偄傞偺偱乯傾僪儗僗偺僨乕僞傪僼僃僢僠偟偰偄傞偺偱丄柦椷偼愗傝懼傢傞偑丅

偝偰夵憿偩丄僼僃僢僠僒僀僋儖偺娫乮俵侾僗僥乕僩乯丄柦椷僨僐乕僟傪僨傿僗僄乕僽儖偵偟偰傒偨丅傆傓傆傓丄偙傟偱偳偆乕乕乕乕偩両丅

偁傝傖偭両摦嶌偟側偄丅傗偭傁傝係俵俫倸偼偩傔偐偹偉丒丒丒丅

傕偺偺偮偄偱偩丄儘僕僢僋傾僫儔僀僓偱妋擣偡傞偲彮偟條巕偑曄傢偭偨丅怣崋偺働儞僇偼柍偔側偭偨傛偆偩偑丄傗偭傁傝傾僪儗僗儔僢僠儈僗偑偁傞丅偙傟偼側傫偠傖丅傾僪儗僗僨乕僞偲儔僢僠怣崋偑摨帪偵偱偰偄傞偧丅偳偆傗傜偆傑偔庢傝崬傔偰偄側偄傛偆偩丅偳偆偟偰俹俠偺弌椡偑抶偄偺偩傠偆丅懠偺晹暘偼栤戣柍偄偺偩偑丅

夞楬恾傪傛乕乕乕乕偔挱傔傞偲丅偁偭丒丒乮偙傟偽偭偐乯丄傕偆堦偮巚偄弌偟偨丅嶐擔偺斢斞偵壗怘偭偨偐朰傟傞偺偱巇曽側偄偐丒丒丒丄偄傗丄巚偄弌偟偨偺偩偐傜柍栤戣偐偀丒丒丒丅

柦椷幚峴姰椆偱儅僔儞僗僥乕僩傪儕僙僢僩偡傞偑丄儕僙僢僩偟偨搑抂偵僼僃僢僠僒僀僋儖偺俿侾僗僥乕僩偵側傞丅偩偑丄帪娫抶傟偑偁傞偺偱俿侾僗僥乕僩偺愭摢偱偼側偄丅偙偺抶傟偑夞楬恾偱偼撉傔側偐偭偨偺偩丅幚嵺偵摦嶌偝偣側偄偲暘偐傜傫丄偲偦偺帪巚偭偨偺傪丄巚偄弌偟偨偺偩丅

尦僋儘僢僋侾俇俵俫倸偲偟偰偄偰丄俀僋儘僢僋傎偳抶傟偰偄傞丅側偺偱侾俀俆ns抶傟偰偄傞偙偲偵側傞丅傾僪儗僗儔僢僠偼俁僋儘僢僋栚偺棫偪忋偑傝傪巊偭偰偄傞偺偱丄傗偼傝侾俀俆ns偱弌傞丅偙傟偱偼偩傔側偺偱丄係僋儘僢僋栚偺棫偪忋偑傝傊曄峏偟偨丅

偦偙偱係俵俫倅偱摦嶌偝偣偰傒傞偲丄側傫偲偆傑偔摦嶌偟偨偺偱偁傞丅係俵俫z偱摦嶌偟偰偔傟傟偽屼偺帤偩丅偄傗乕乕婐偟偄側偀丅偱傕丄柦椷幚峴晹傪捛壛偟偰偄偭偰俬俠偑憹偊丄攝慄偑憹偊丄晜梀梕検偑憹偊傞偲丄摦嶌偟側偔側傞偐傕偟傟側偄丅偸偐婌傃偵側傜側偗傟偽椙偄偑丅

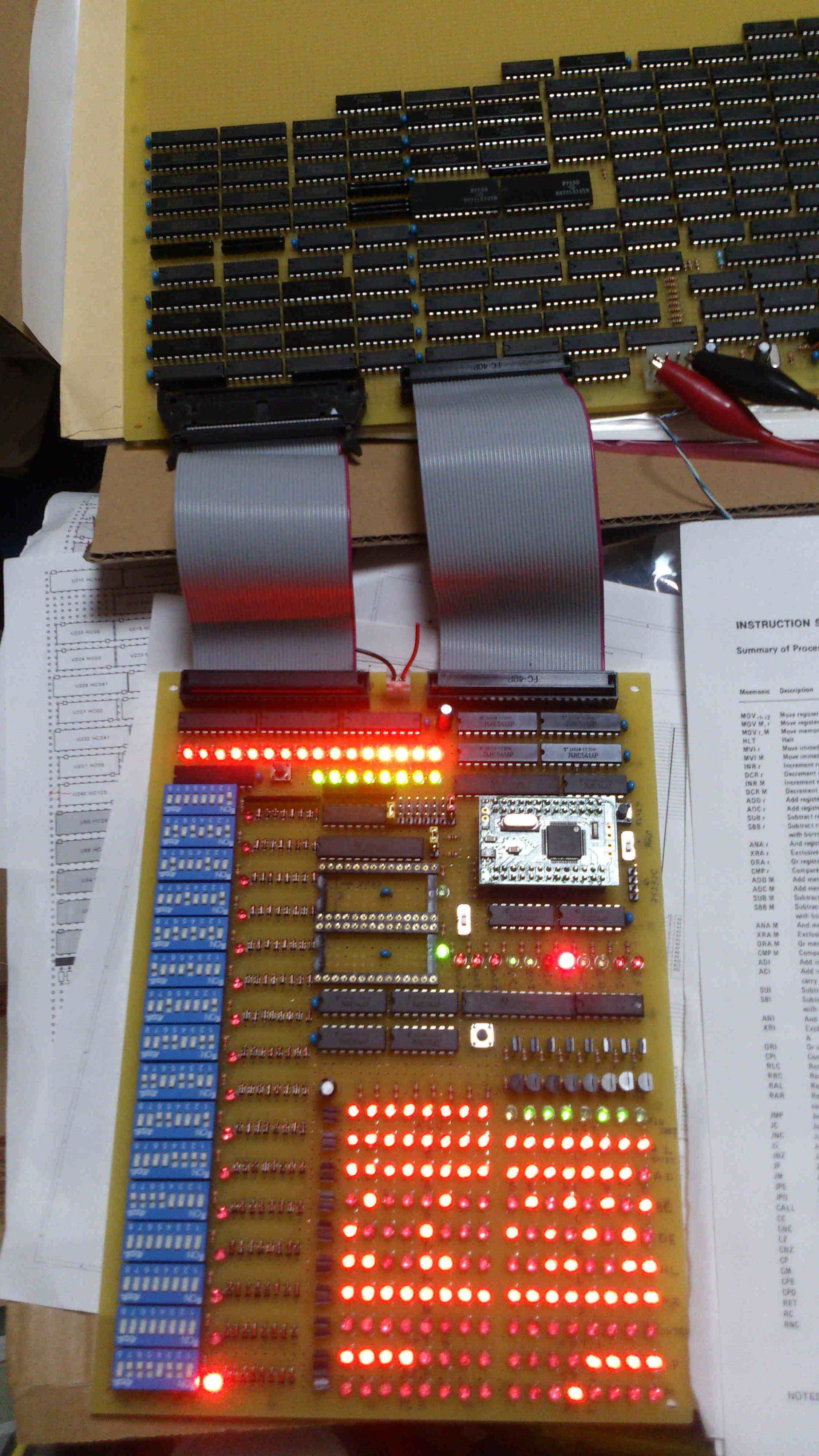

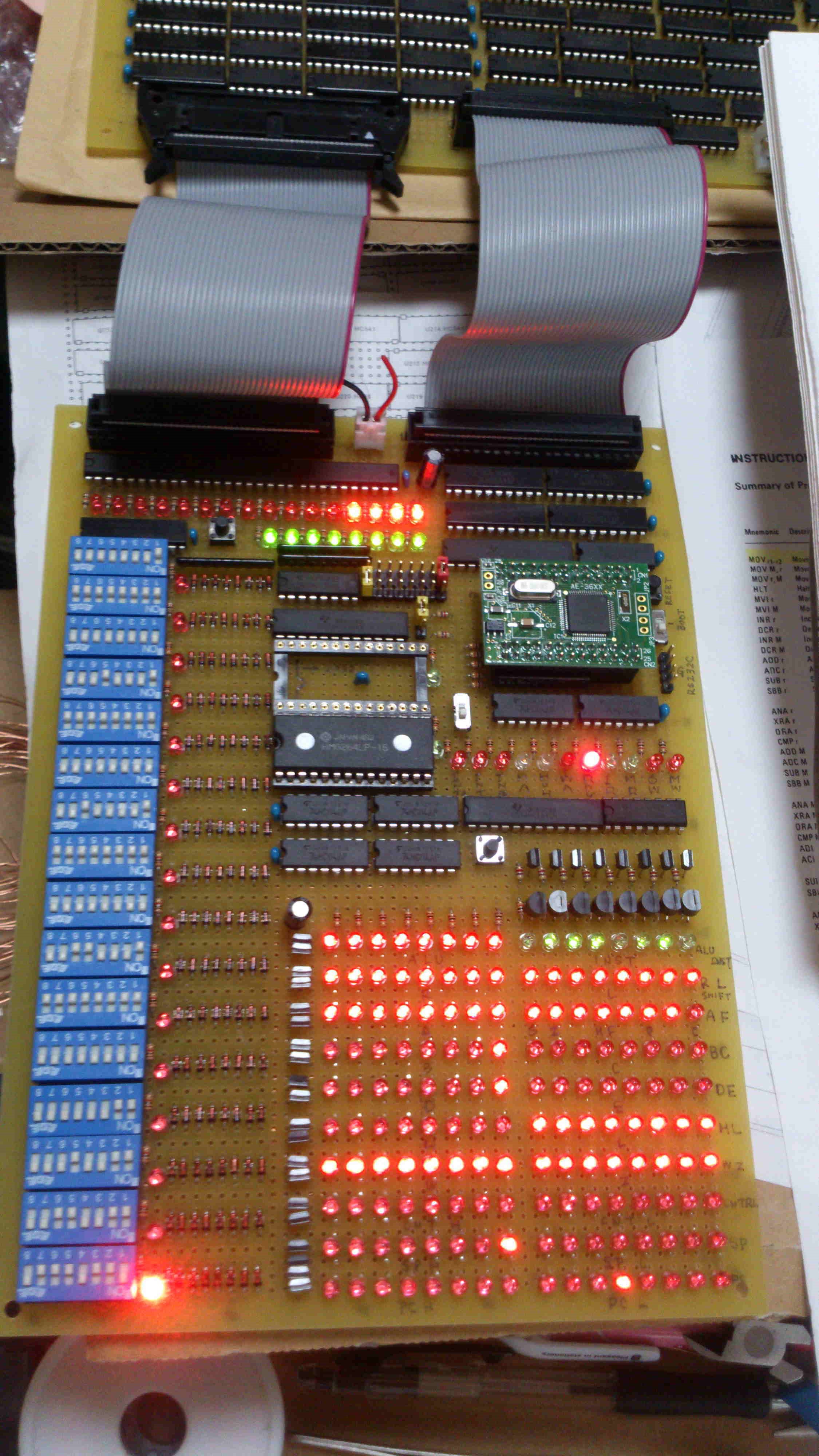

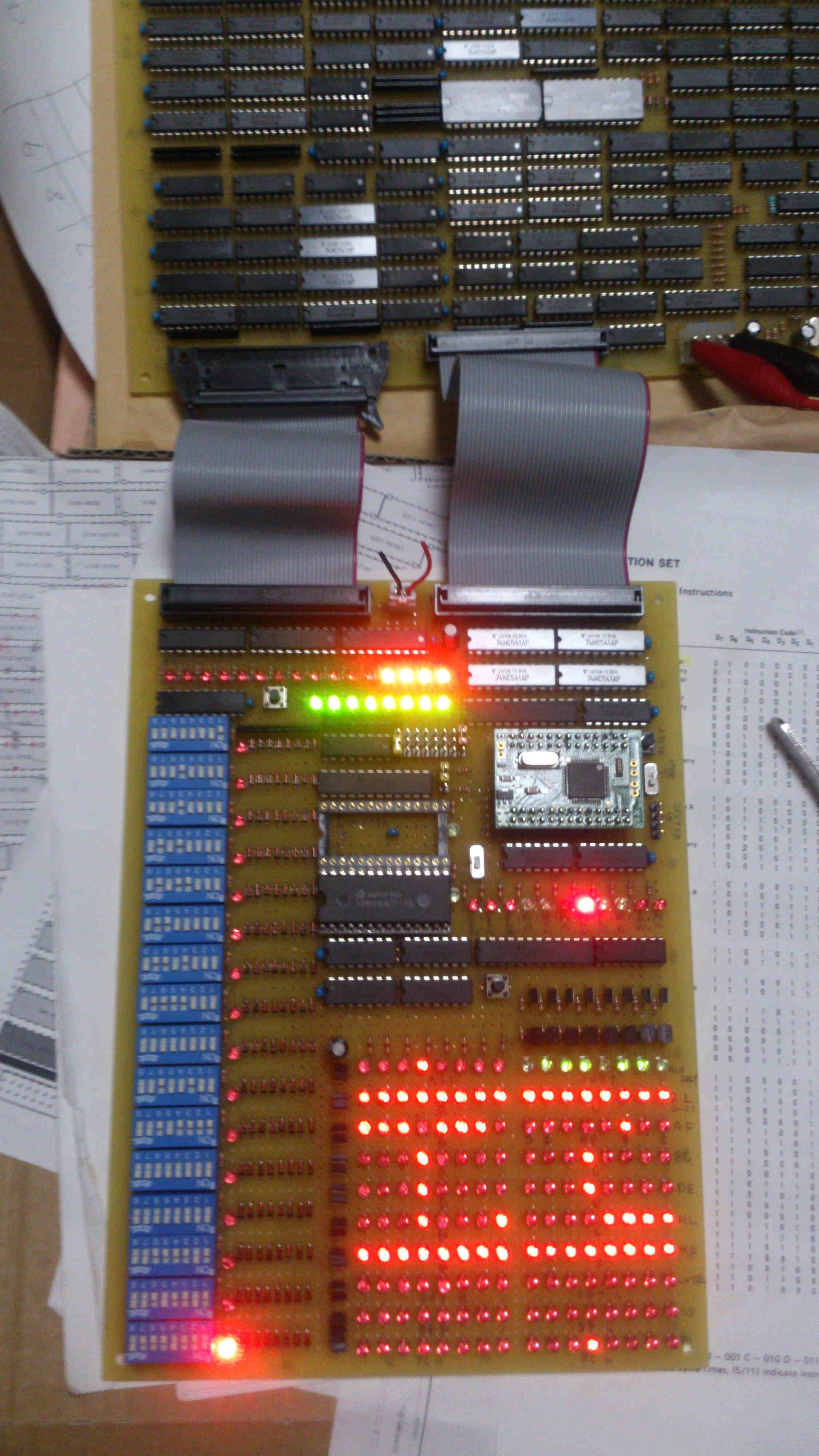

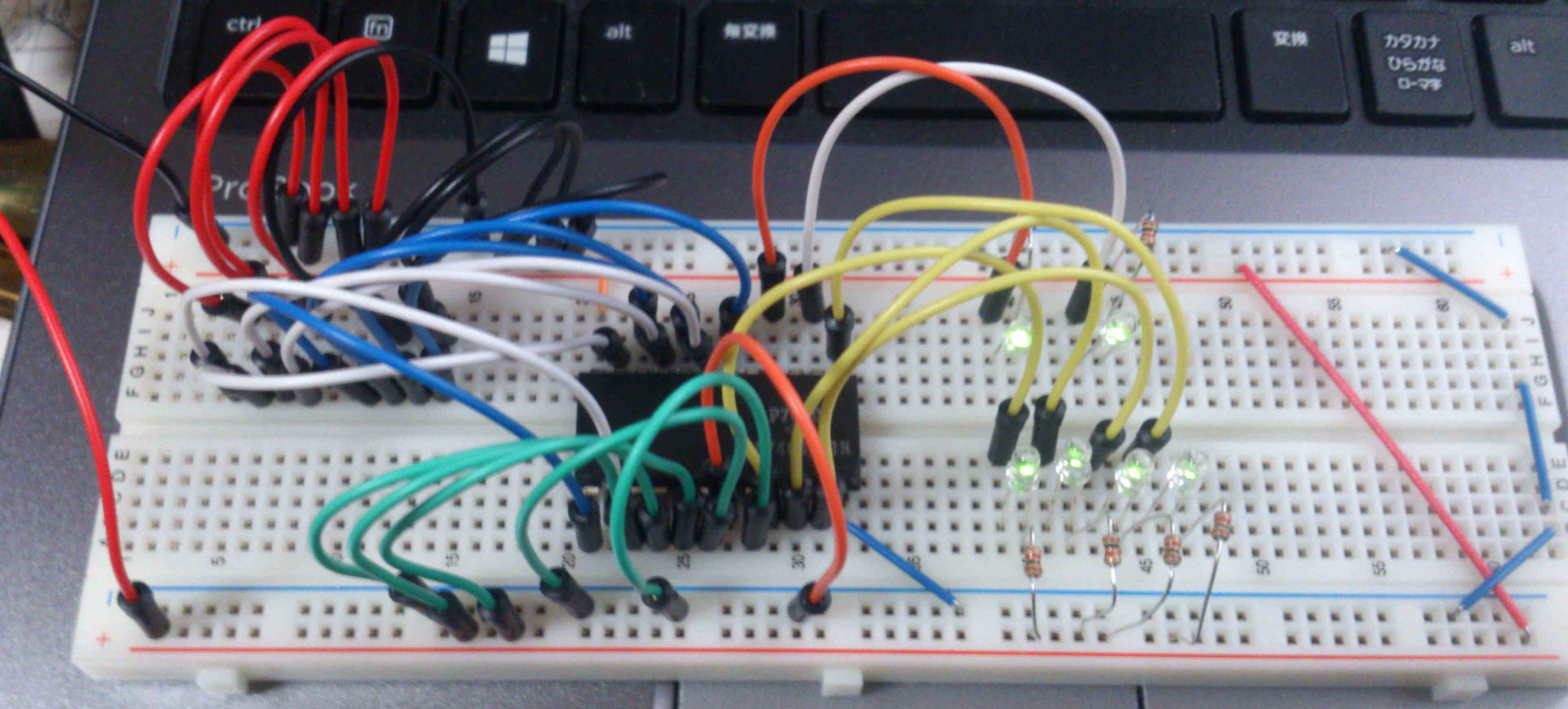

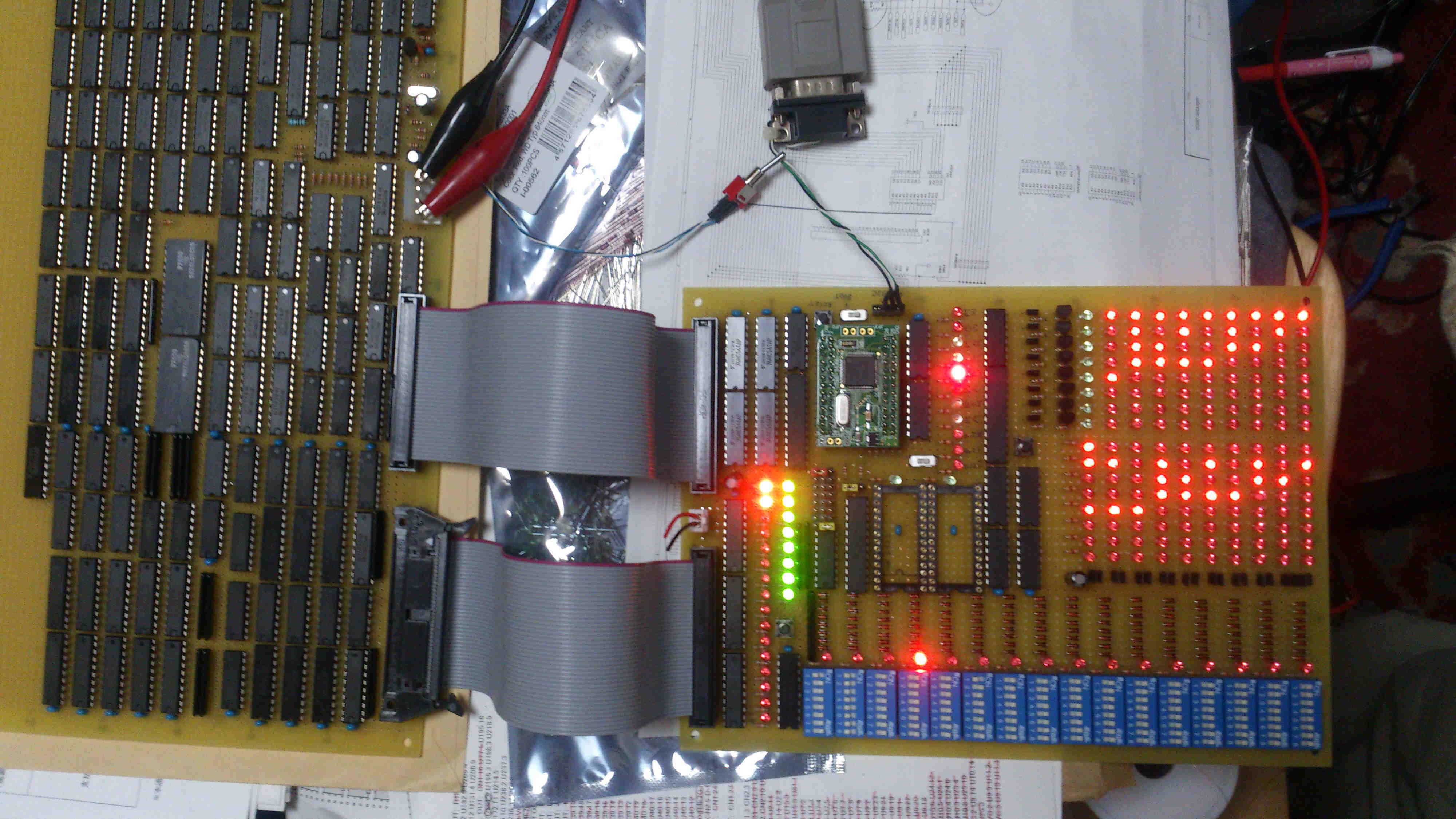

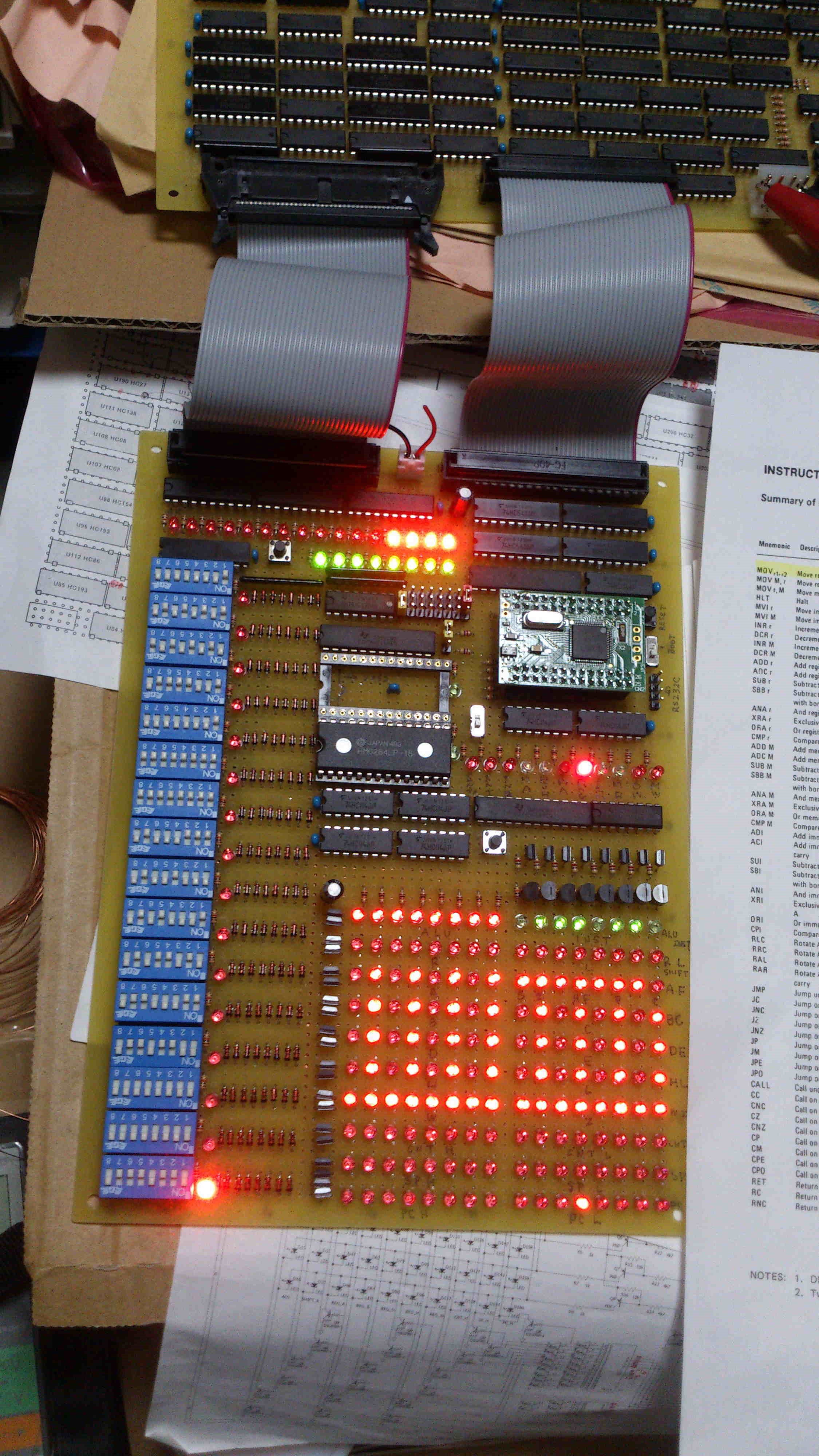

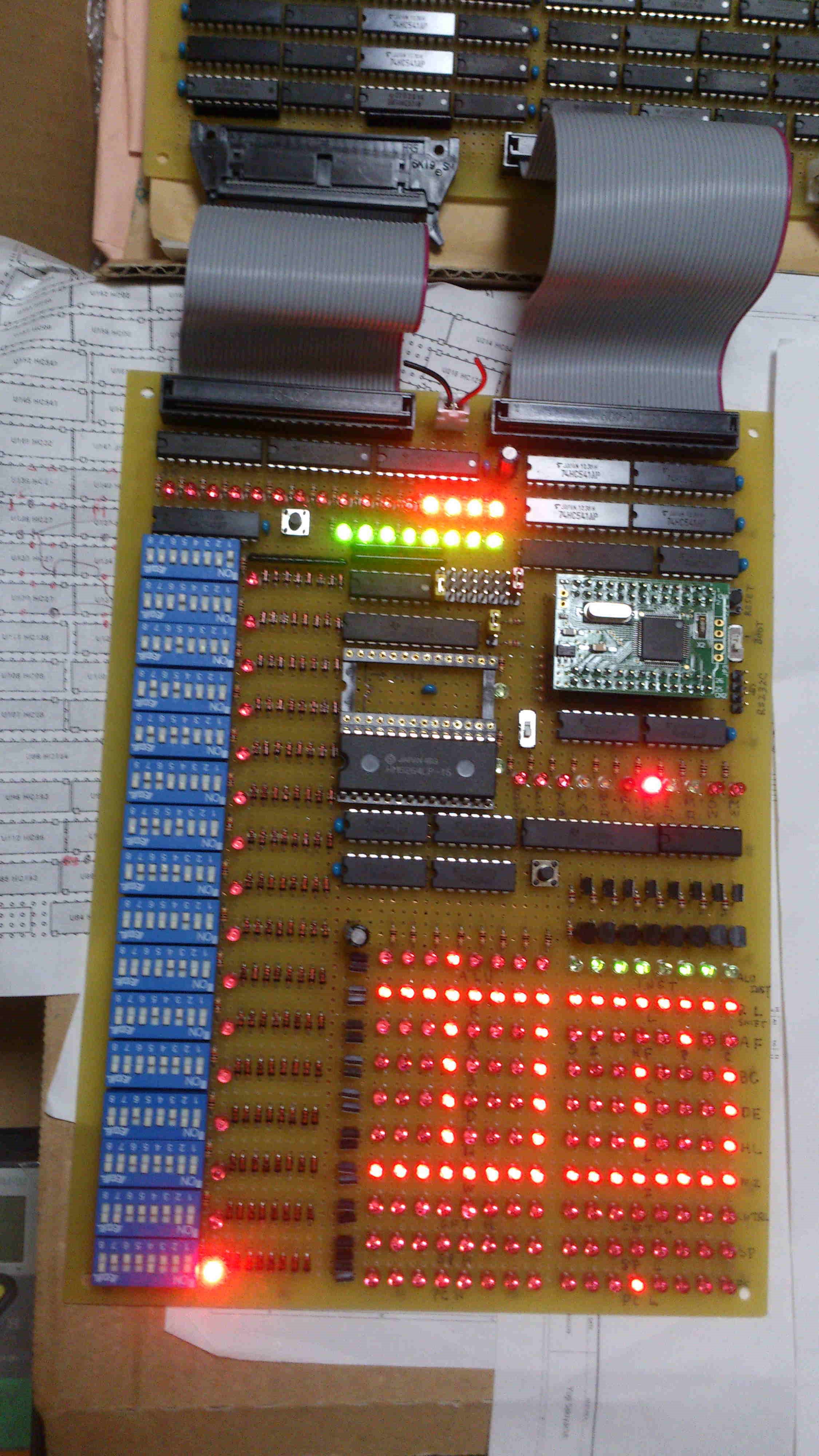

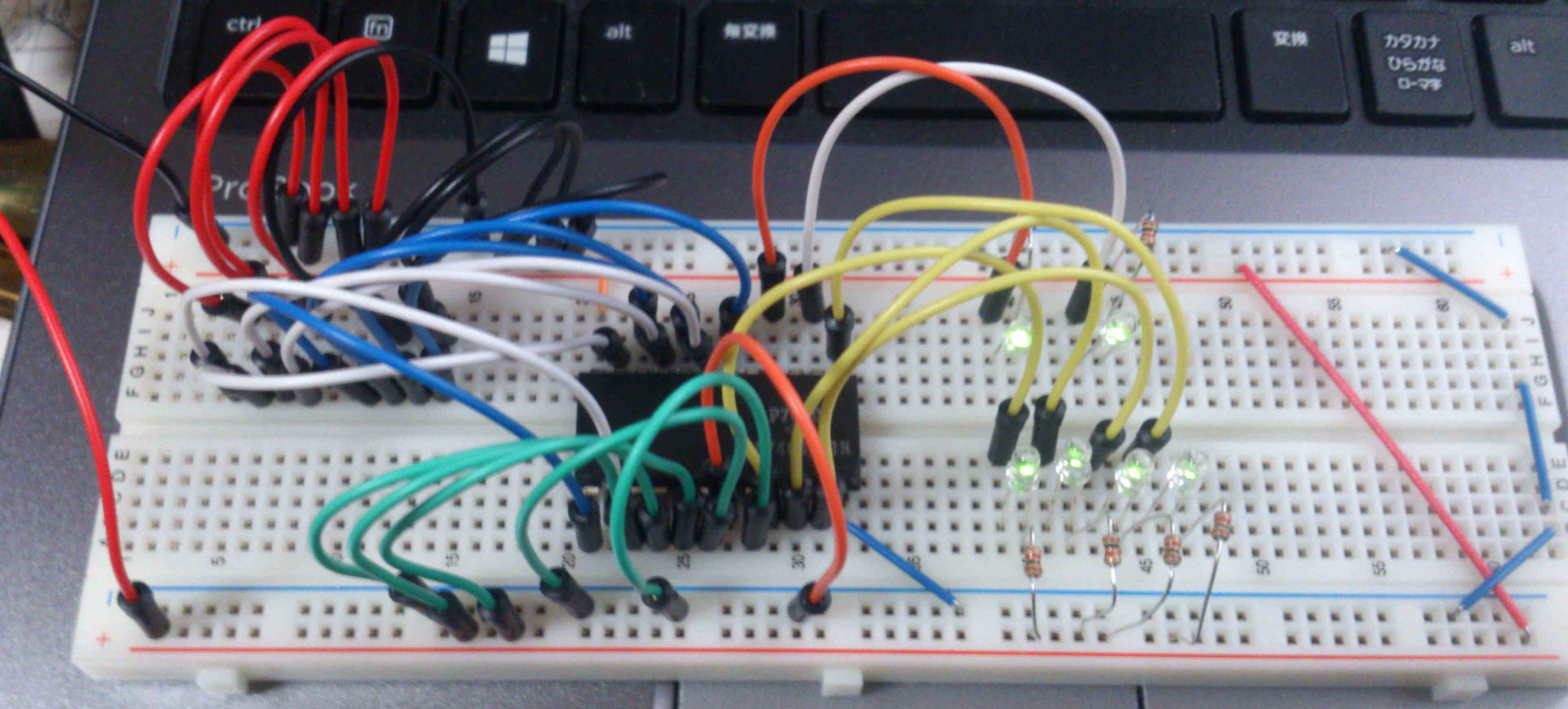

僋儘僢僋係俵俫倸偱摦嶌偟偨帪偺幨恀乮仸屻擔捛婰丗俿値僋儘僢僋傪係俵俫倸偱嶌偭偰偄傞偺偱係俵俫倸偲彂偄偰偟傑偭偨偑丄俿値偺廃攇悢偼敿暘偺俀俵俫倸偲側傞丅偳偆傗傜偙傟偑俠俹倀僋儘僢僋偺傛偆偱偁傞乮娋乯丅側偺偱倝俉侽俉侽偺俀俵俫倸偲摨摍偱偁偭偨丅乯

俀侽侾俈擭俇寧枛

丂俽俿俙倃丄俴俢俙倃柦椷傪捛壛偟摦嶌妋擣俷俲丅偙傟偼妝彑偩偭偨丅懕偄偰俵俷倁柦椷丄俵俷倁丂倰丄倰偱偁傞丅捛壛姰惉偟偰丄摨偠偔妝彑偲巚偄偒傗丄俙儗僕埲奜偼偆傑偔摦嶌偡傞丅偆傑偔摦嶌偟側偄偺偼俙儗僕傊擖傟傞応崌偩丅俵俷倁丂俙丆倰丂偑偆傑偔摦嶌偟側偄丅偆乕乕傫丄傑偨傗偭偰偟傑偭偨丅俉價僢僩僶僗偵宷偑偭偨俙儗僕僗僞偲俛丆俠側偳偺儁傾儗僕僗僞偺侾俇價僢僩僶僗偺僨乕僞儖乕僩偺愗傝懼偊偱儈僗偭偰偄偨丅儗僕僗僞巜掕偺倰偑嬼悢偺応崌丄俛丄俢丄俫儗僕僗僞偲側傝丄婏悢偺応崌偼俠丄俤丄俴儗僕僗僞偲側傞丅側偺偱俵俷倁柦椷偺俽倧倳倰們倕偲俢倕倱倲倝値倎倷倝倧値偑嬼悢偳偆偟丄婏悢偳偆偟偼偦傟偧傟偺俉價僢僩僶僗撪偩偑丄堘偆慻傒崌傢偣偱偼丄嬼悢仼婏悢丄婏悢仼嬼悢偺応崌偼偦傟偧傟偺俉價僢僩僶僗僨乕僞傪傕偆曅曽傊憲傞傛偆偵僎乕僩傪愗傝懼偊傞傛偆偵偟偰偄傞丅偩偑丄俢倕倱倲倝値倎倲倝倧値偺俙儗僕僗僞偼婏悢偩偑丄侾俇價僢僩僶僗懁偱偼側偔丄嵟弶偵彂偄偨傛偆偵俉價僢僩僶僗懁偵偁傞偺偩丅側偺偱偦偪傜懁傊僨乕僞憲傜側偗傟偽側傜側偄丅偦偙偑敳偗偰偄偨丅偆乕乕乕傫丅俬俠侾屄捛壛偩丅岾偄夞楬尒捈偟偱侾屄晄梫偵側偭偨晹暘偑偁傞偺偱丄偦偙偵幚峴晹偺傑偩幚憰偟偰偄側偄俬俠傪偢傜偟偰僗儁乕僗傪嶌傝侾屄捛壛偟偨丅

偙傟偱俵俷倁丂倰丆倰柦椷偑姰惉偟偨丅乮傗傟傗傟乯

俵俷倁偺僥僗僩柦椷

俴倃俬丂俛丄侽俙俙俆俆俫

俵俷倁丂俙丄俠

俴倃俬丂俛丄侽俥俥俥俥俫

俵俷倁丂俛丄俙

俵俷倁丂俠丄俛

俵俷倁丂俢丄俠

俵俷倁丂俤丄俢

俵俷倁丂俫丄俤

俵俷倁丂俴丄俫

俫俴俿

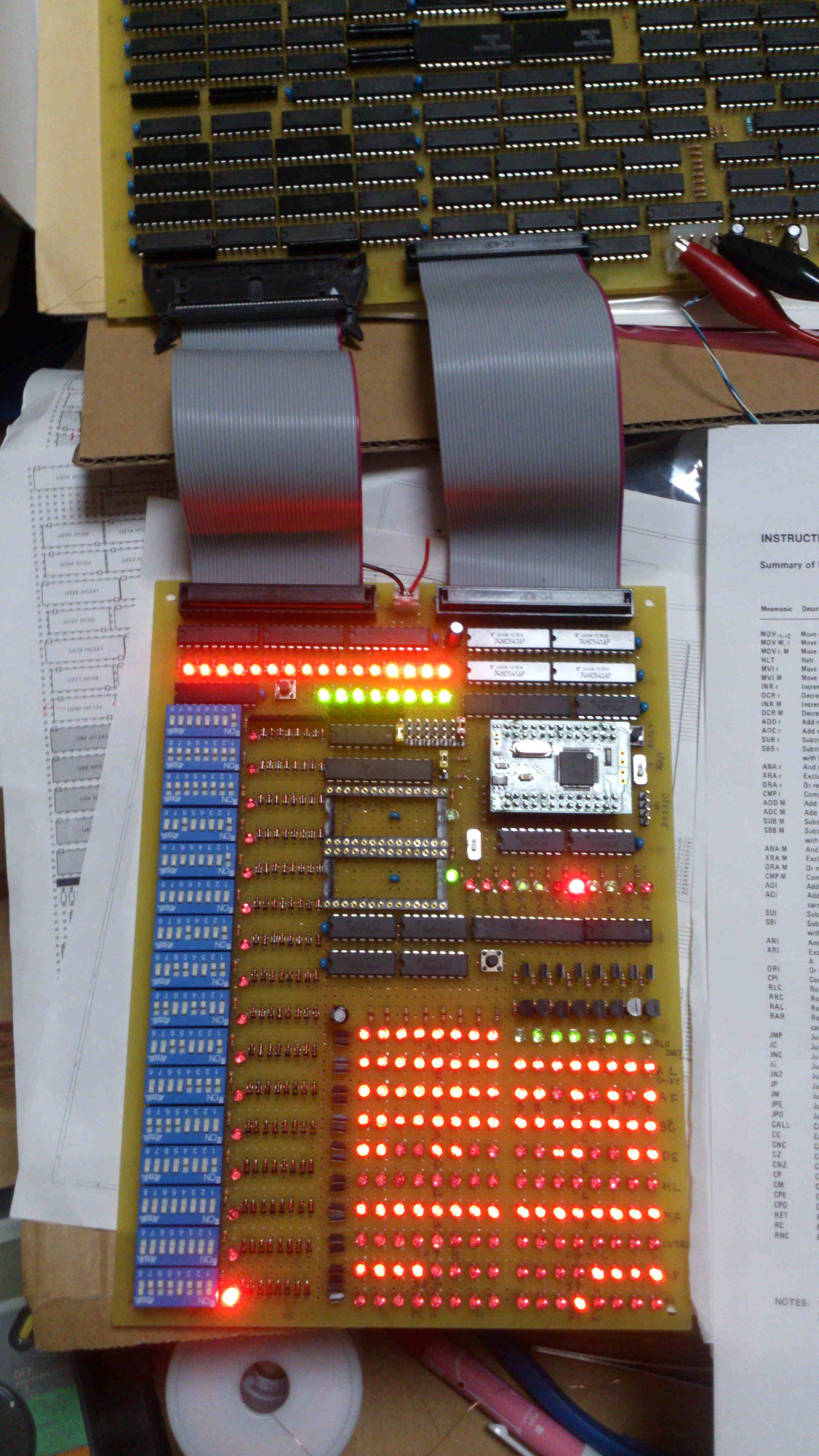

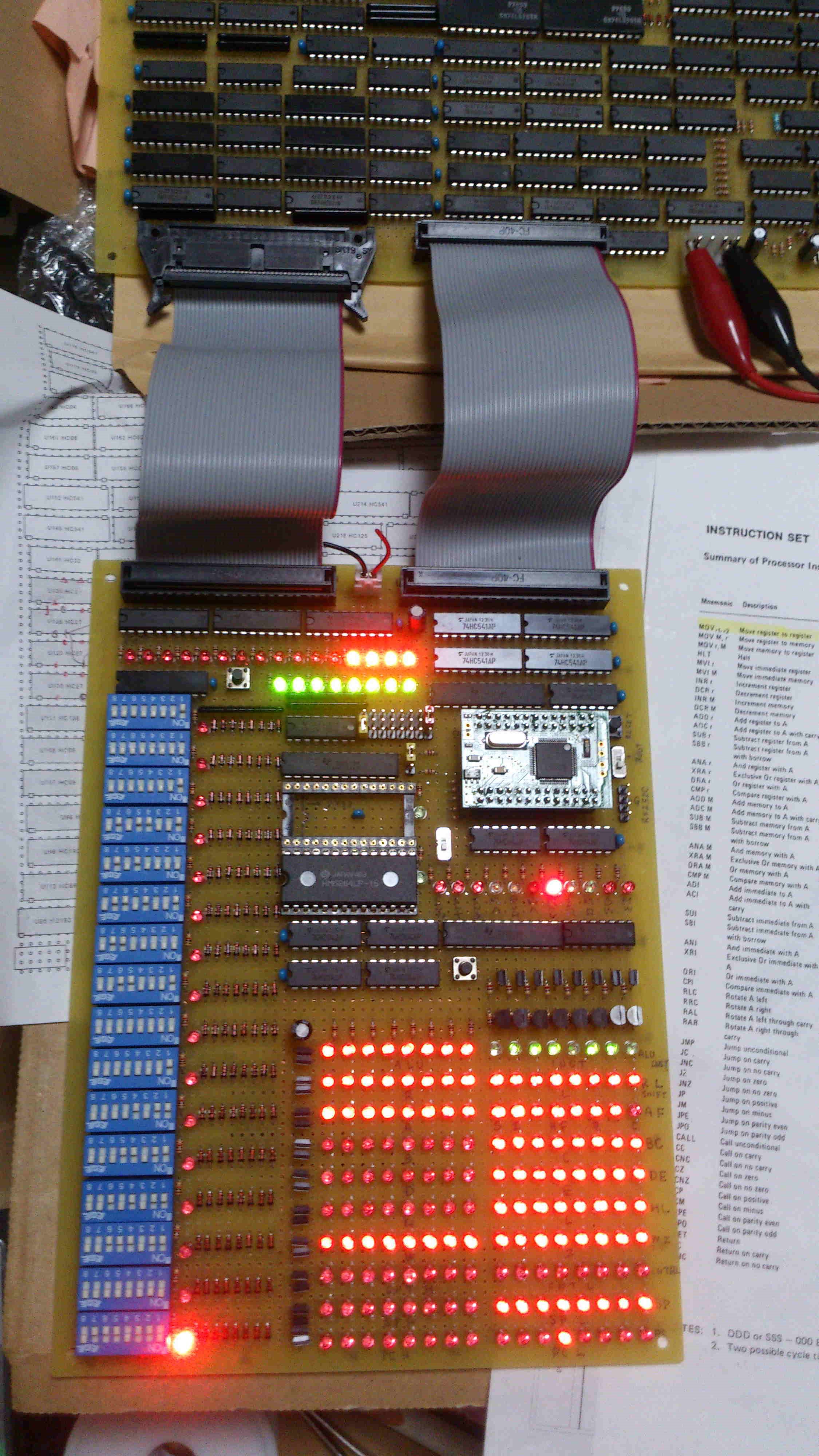

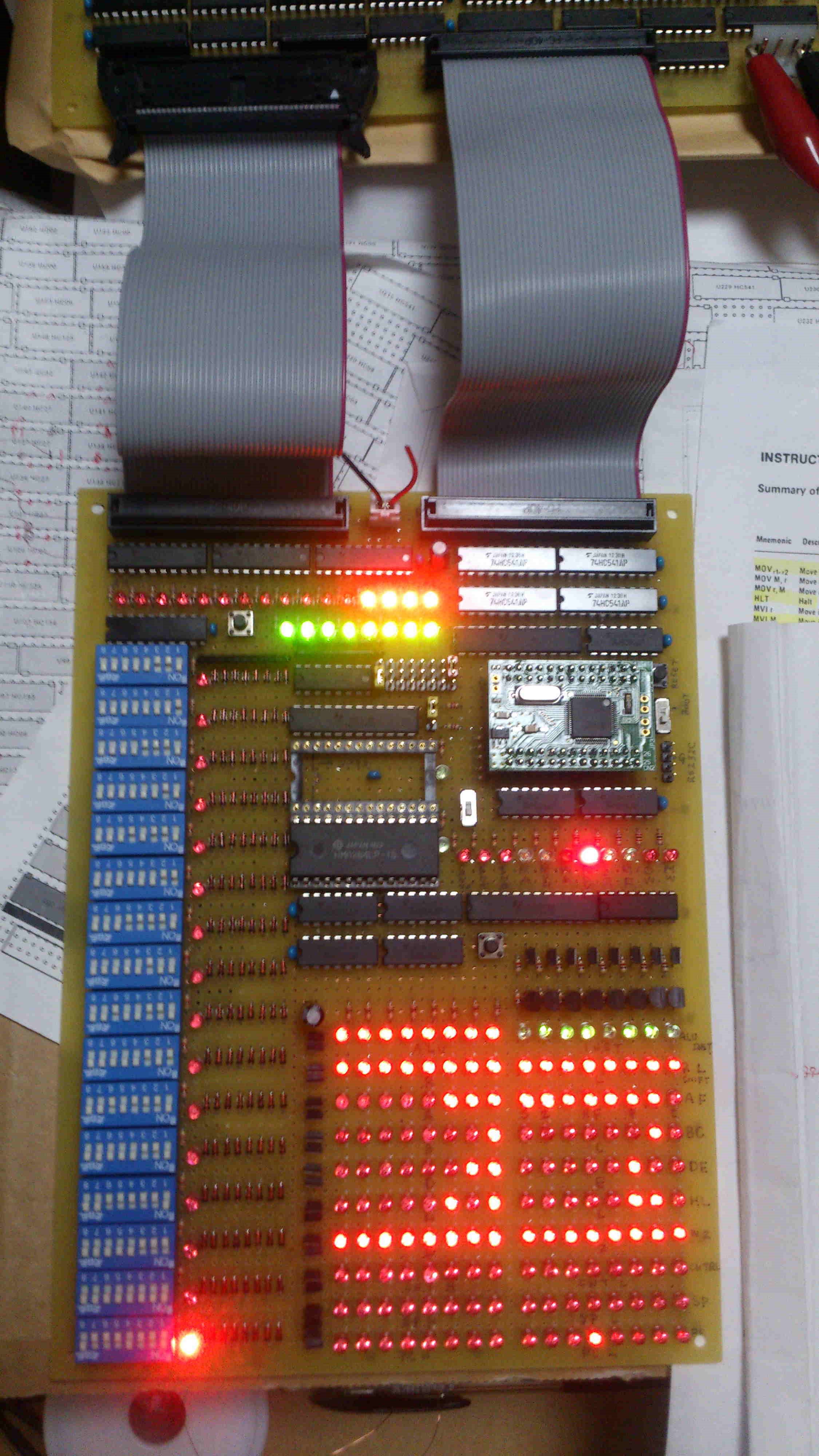

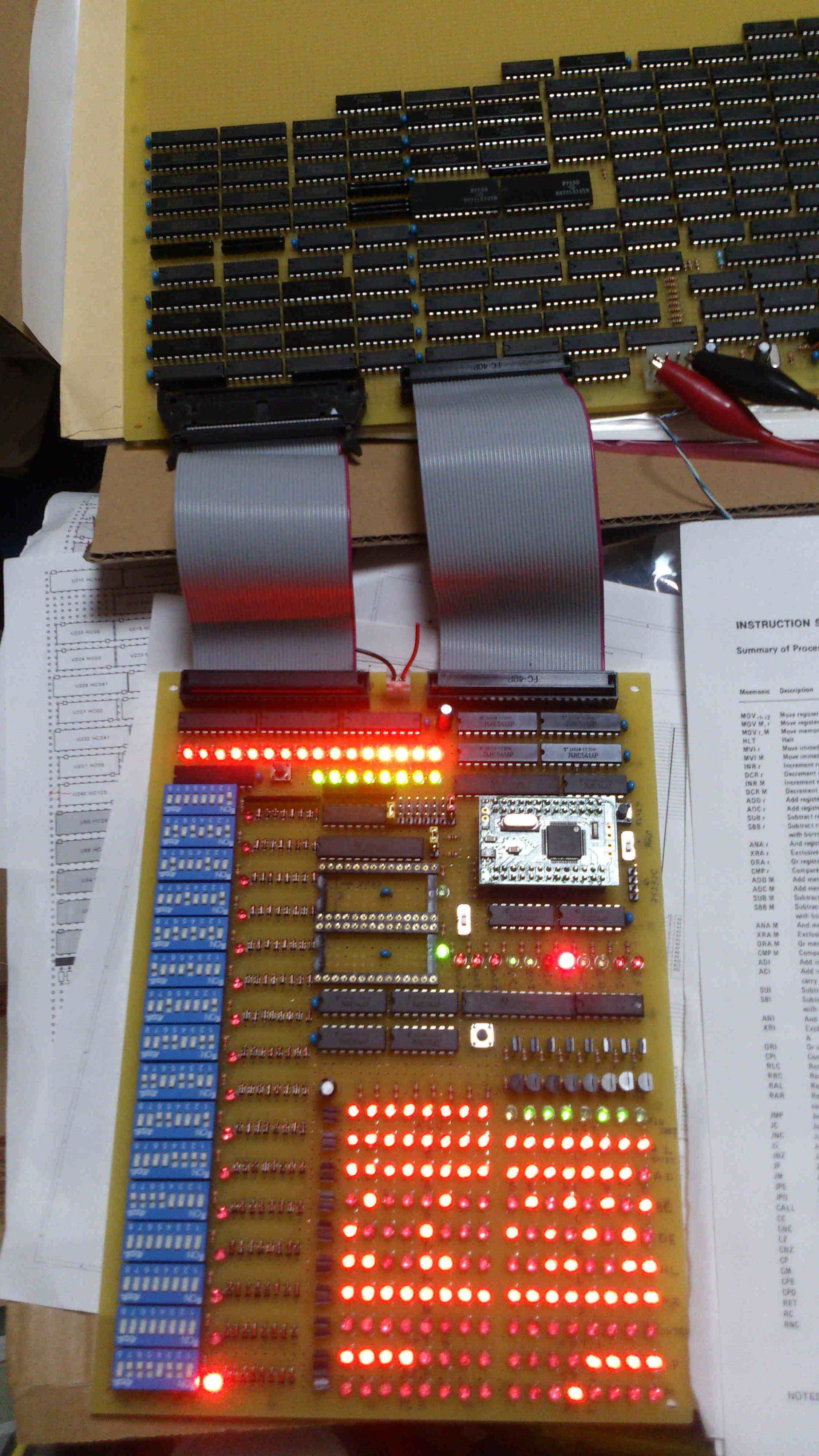

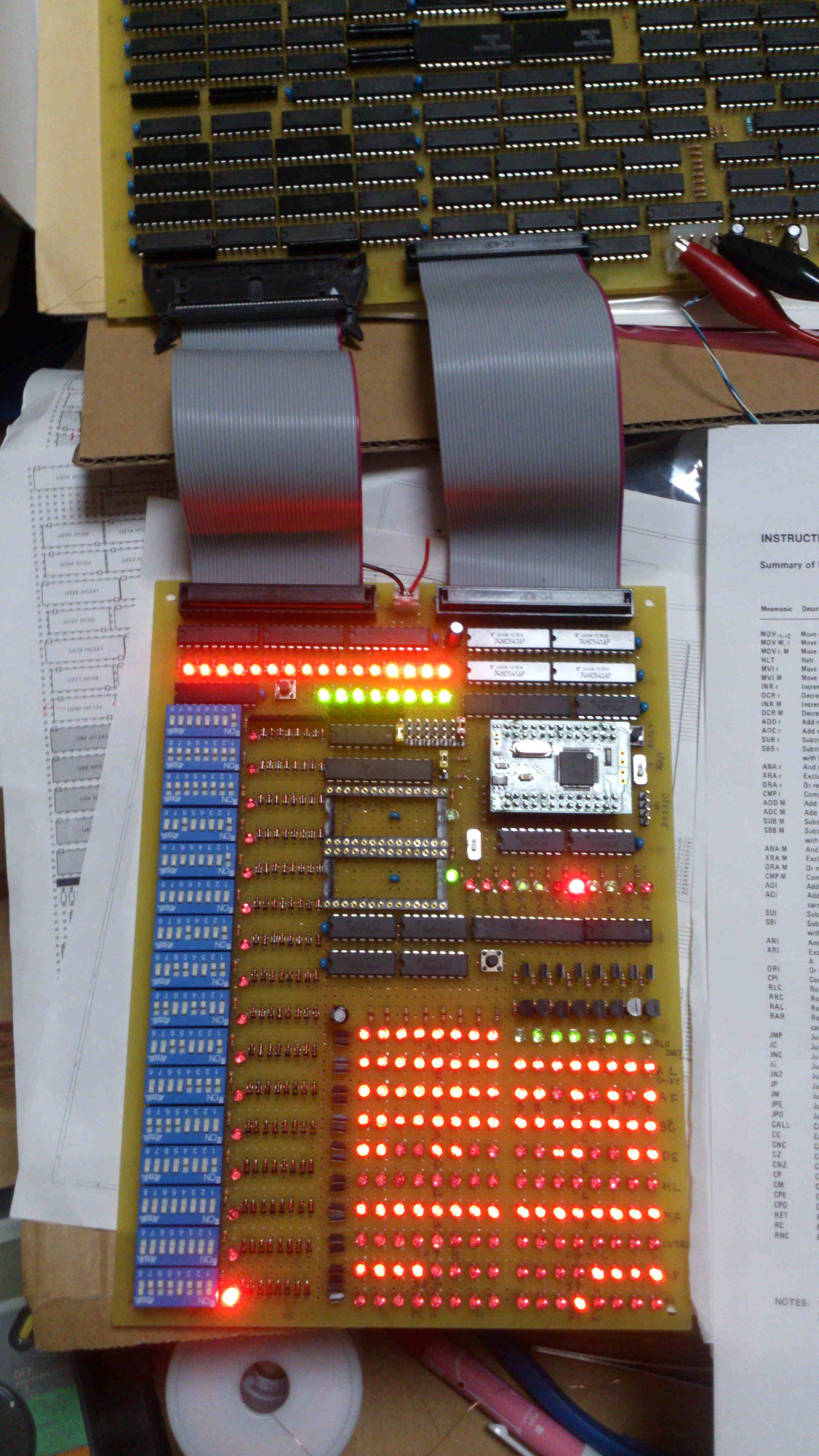

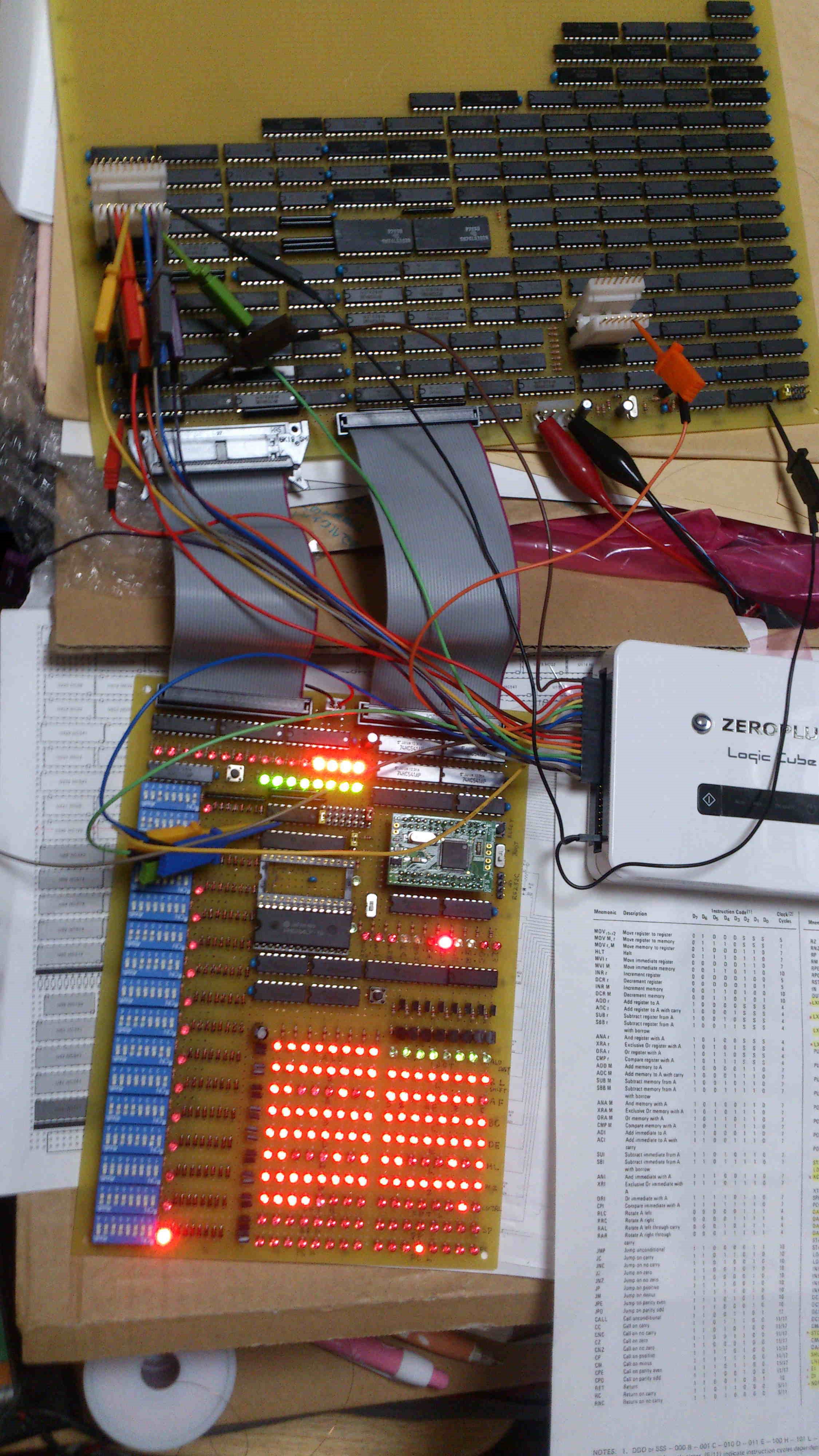

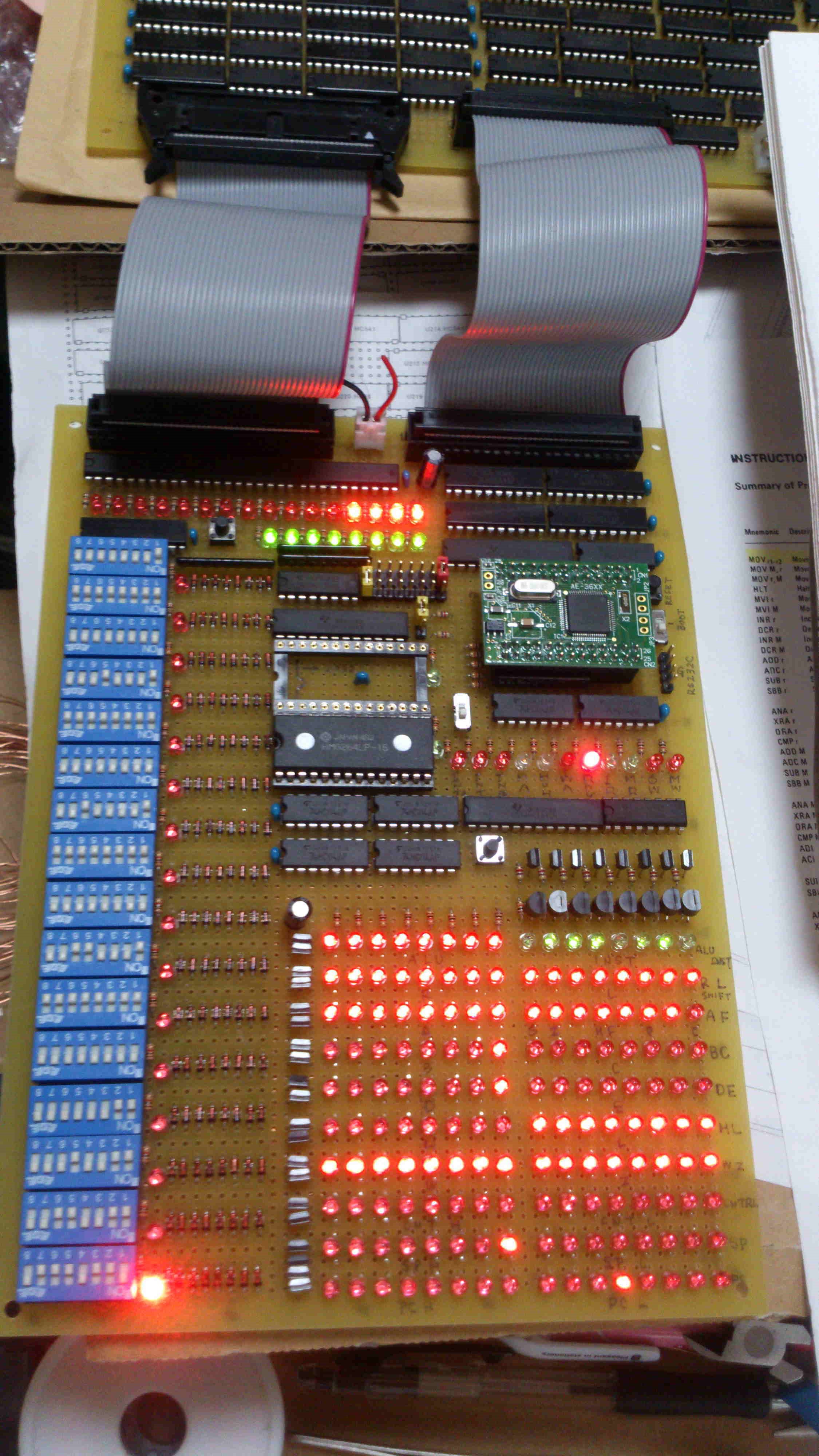

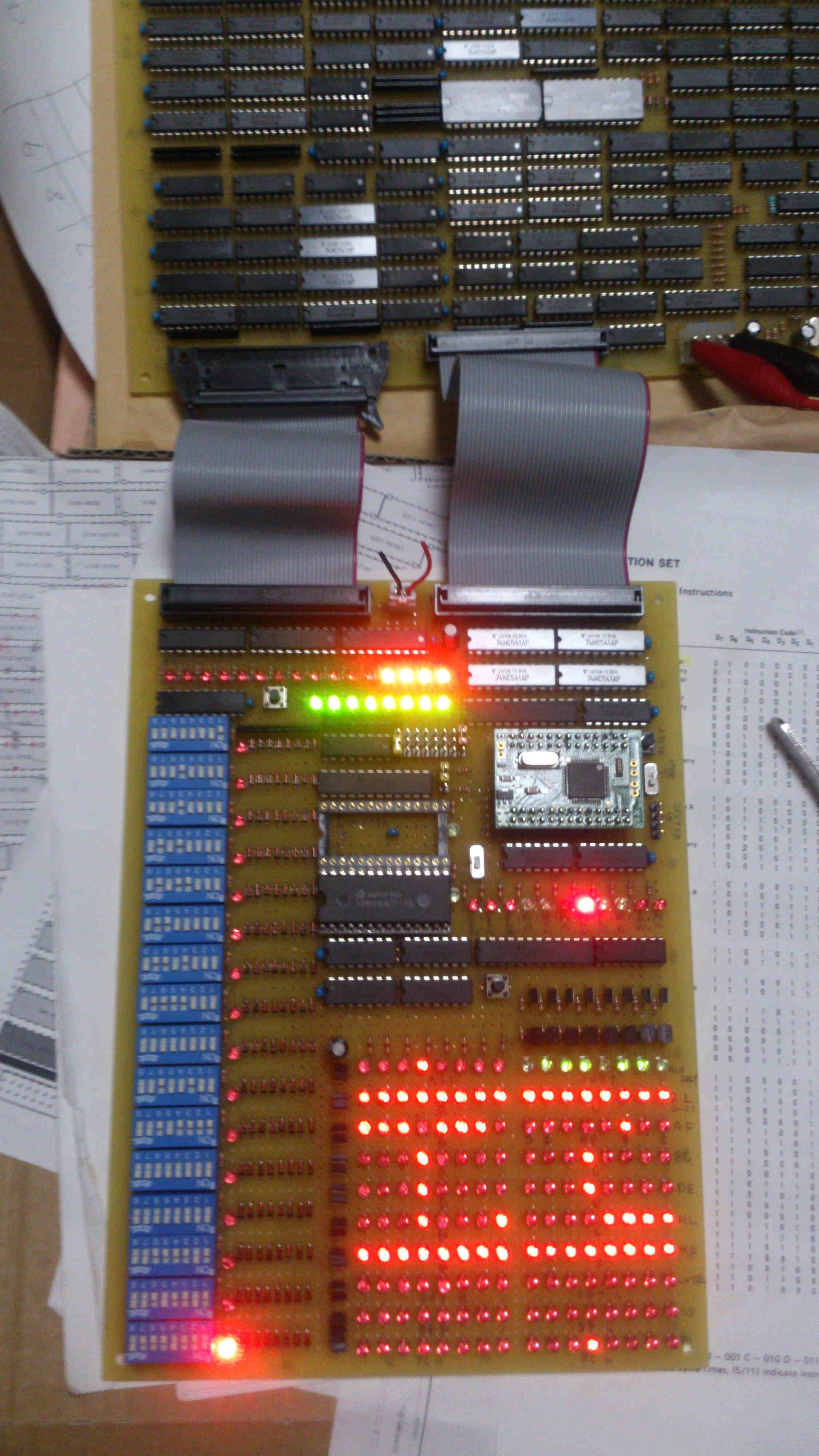

幚峴寢壥偺幨恀

柦椷傪侾屄偯偮捛壛偡傞偺偼柺搢偩偲巚偭偰傕傒偨偑丄偙偆偄偆帠偑桳傞偺偱傗偼傝柦椷偼侾屄偯偮捛壛偡傞帠偵偟傛偆丅乮傗偭傁傝乯丅

俀侽侾俈擭俈寧弶弡

丂捛壛偱偒偨柦椷偼俬俶倃偲俠俵俙丄俢俙俙偱偁傞丅

僥僗僩

傑偢偼

俴倃俬丂俛丆侽侽俥俥俫

俴倃俬丂俢丆侽侽俥俥俫

俴倃俬丂俫丆侽侽俥俥俫

俴倃俬丂俽俹丆侽侽俥俥俫

俬俶倃丂俛

俬俶倃丂俢

俬俶倃丂俫

俫俴俿

偲偟偨丅俬俶倃丂俽俹傕擖傟偨偐偭偨偑侾僶僀僩懌傜側偄丅俬俶倃丂俫傪俬俶倃丂俽俹偵曄偊偰俀夞僥僗僩偡傞丅

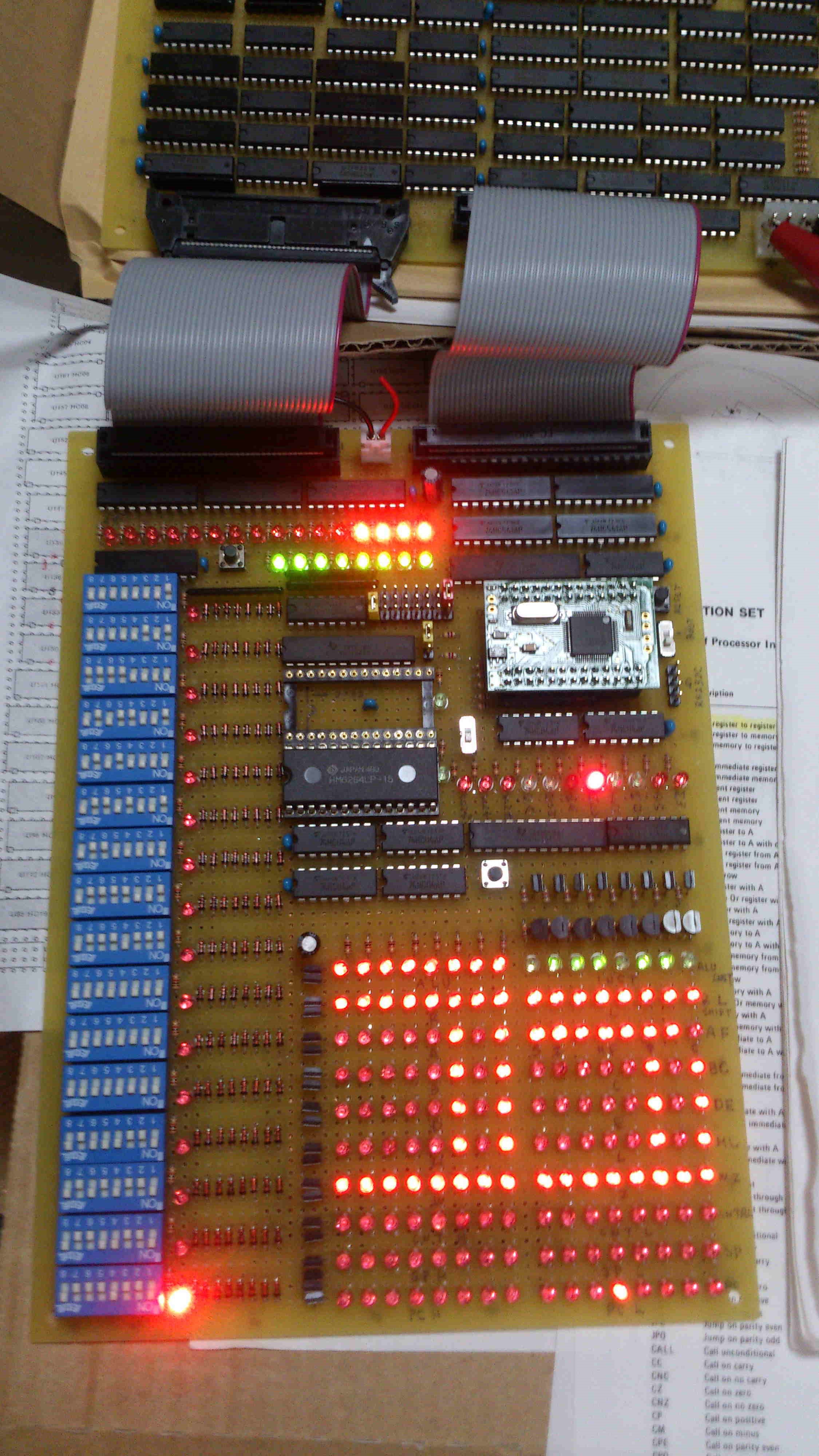

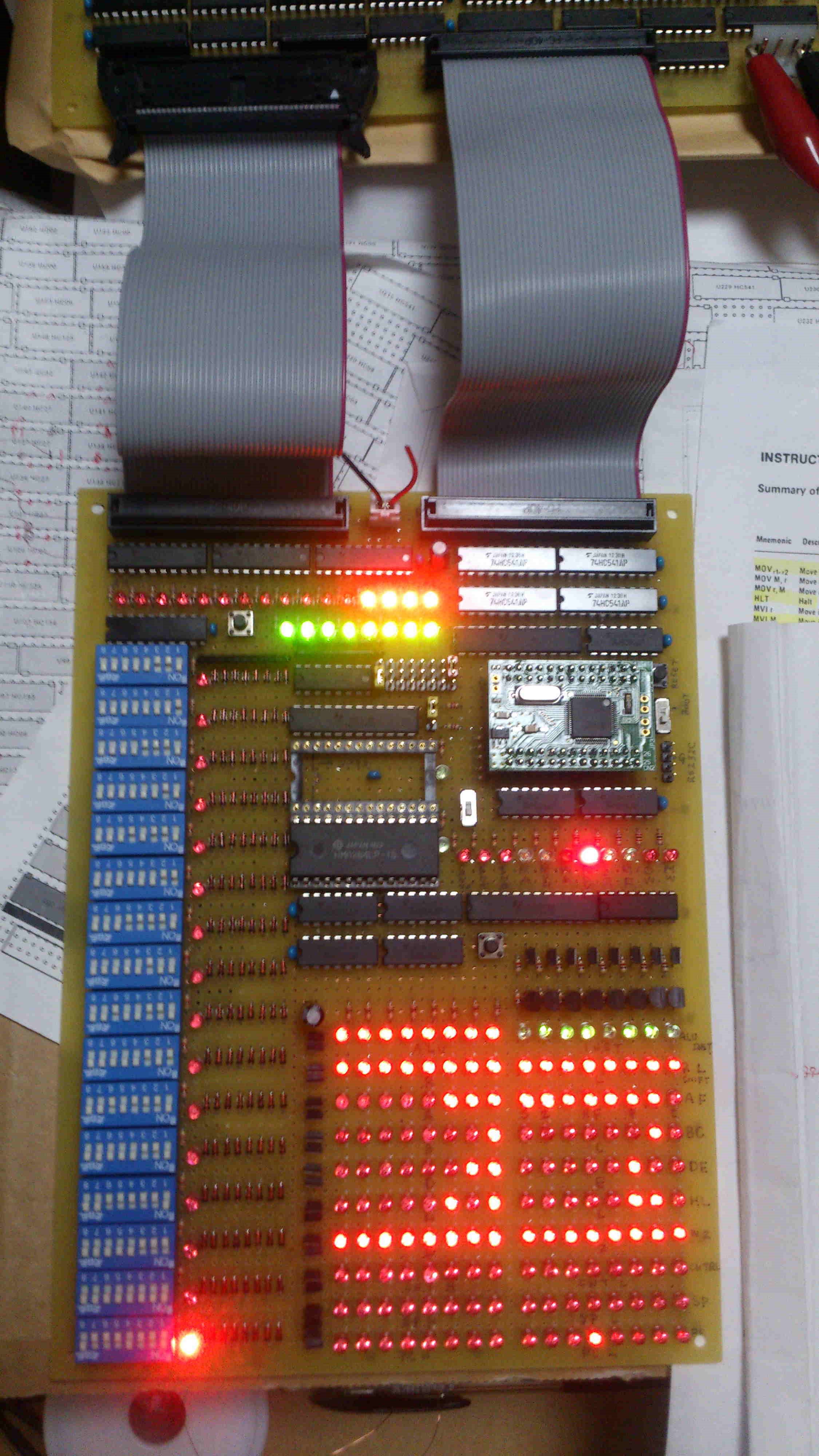

俬俶倃丂俽俹偵曄偊偰僥僗僩偟偨幨恀丅

師偵俠俵俙偲俢俙俙偺僥僗僩丅

俴倃俬丂俛丆侽侽俆俆俫

俵俷倁丂俙丆俠

俠俵俙

俫俴俿

偱俙儗僕僗僞偑俙俙俫偵側傞偙偲傪妋擣丅

偙傟偵俢俙俙傪捛壛偡傞偲

俙俠僼儔僌偲俠僼儔僌俷俶偟偰偄偨偺偱丄侾侽俫偲側傝俠僼儔僌偑俷俶偟偰偄傞丅

庢傝姼偊偢摦嶌偟偰偄傞傛偆偱偁傞丅

偱傕偙偺儁乕僗偩偲偍杶媥傒傑偊偵偼姰惉偟偦偆偵側偄丅

侾侾寧偙傠姰惉偐側偀丒丒丒丅偙傟偩偲夞楬恾傪彂偒偼偠傔偰侾擭偐偐偭偨偙偲偵側傞丅偁傢偰偰嶌傞昁梫傕柍偄偺偱偺傫傃傝嶌傞偐丒丒丒丅

偁丄偦偆偩偭偨丅俢俠倃傕偱偒偰偄傞偺偩偭偨丅俬俶倃偲俢俠倃偼傎偲傫偳摨偠偱丄亄侾偡傞偐亅侾偡傞偐偺堘偄側偺偱傎傏嫟捠夞楬偱偱偒傞偺偩丅幨恀傪嶣傝朰傟偰偄偨偺偱丄彂偒朰傟偰偄偨丅

夵傔偰幨恀傪嶣傝捈偟偨丅

儗僕僗僞偵摨偠僨乕僞傪擖傟傞側傜俴倃俬傪暲傋傞傛傝俵俷倁傪巊偭偨曽偑柦椷僶僀僩悢偑彮側偔偰偡傓丅

偲尵偆偙偲偱幚峴偟偨柦椷偼

俴倃俬丂俛丆侽侾侽侽俫

俵俷倁丂俤丆俠

俵俷倁丂俢丆俛

俵俷倁丂俴丆俠

俵俷倁丂俫丆俛

俴倃俬丂俽俹丆侽侾侽侽俫

俢俠倃丂俛

俢俠倃丂俢

俢俠倃丂俫

俢俠倃丂俽俹

俫俴俿

偙傟傪幚峴偡傞偲慡偰偺儗僕僗僞偺抣偼侽侽俥俥俫偲側傞丅

俀侽侾俈擭俈寧拞

丂俵俷倁丂倰丄俵偲俵俷倁丂俵丆倰偑偱偒偨丅

憗懍僥僗僩偩丅

俴倃俬丂俛丆侽俥侽侽俆H

俵俷倁丂俤丆俠

俵俷倁丂俢丆俛

俵俷倁丂俴丆俠

俵俷倁丂俫丆俛

俵俷倁丂俵丆俠

俵俷倁丂俛丆俵

俵俷倁丂俢丆俵

俵俷倁丂俙丆俵

俵俷倁丂俫丆俵

俫俴俿

偲偟偨丅偙傟偱慡晹偺儗僕僗僞偑侽俆俫偵彂偒姺傢偭偨丅偟傔偟傔丄偱偒偨偧乣丅

偣偭偐偔側偺偱俠丆俤丆俴儗僕僗僞偵彂偔俵俷倁傪俫俴俿傪彍偄偰捛壛偟偨丅

偳乕乕偩偲幚峴偝偣偨偑丒丒丒丒丅偁傝傖乣丅俠丆俤丆俴儗僕僗僞偑侽俆俫偵側傜側偄丅丠丠丠丅

壗屘丠丅俠丄俤丆俴懁傊僨乕僞偑峴偐側偄丠

忋偵彂偄偨俛丆俢丆俙偺強傪俠丆俤丆俴偵偡傞偲偆傑偔摦嶌偟偨丅偟偽傜偔擸傫偩偑丒丒丒丒丅両傂傜傔偄偨両両

傕偆堦搙椻惷偵柦椷傪尒傞偲丅

俴倃俬丂俛丆侽俥侽侽俆H

俵俷倁丂俤丆俠

俵俷倁丂俢丆俛

俵俷倁丂俴丆俠

俵俷倁丂俫丆俛

俵俷倁丂俵丆俠

俵俷倁丂俛丆俵

俵俷倁丂俢丆俵

俵俷倁丂俙丆俵

俵俷倁丂俫丆俵

俵俷倁丂俠丆俵

俵俷倁丂俤丆俵

俵俷倁丂俴丆俵

俫俴俿

傕偆偍暘偐傝偐側丅俴偵摨偠僨乕僞擖傟偰偳偆偡傫偹傫丒丒丒偲尵偆撍偭崬傒偼柍偟丅栤戣偼俵俷倁丂俫丆俵偺埵抲偱偁傞丅偙偺柦椷傪幚峴偡傞偲丄俫亖侽俆俫偲側傞乮摉偨傝慜乯丅

偮傑傝丄偙偺屻偺俵偺傾僪儗僗偼侽俆侽俆俫偲側偭偰俼俙俵偺柍偄乮偲尵偆偐壗傕柍偄乯傾僪儗僗傪撉傒弌偟偨偺偱偁偭偨丅偙偺柦椷傪堦斣嵟屻偵帩偭偰偒偰丄傔偱偨偟傔偱偨偟偲側偭偨偺偱偁傞丅

偦偺屻俵俷倁丂俵丆俙側偳奺儗僕僗僞偐傜俵傊彂偔柦椷傪僥僗僩偟偨丅

俴倃俬丂俛丆侽俥侽侽俆H

俵俷倁丂俤丆俠

俵俷倁丂俢丆俛

俵俷倁丂俴丆俠

俵俷倁丂俫丆俛

俵俷倁丂俙丆俠

俵俷倁丂俵丆俙

俵俷倁丂俢丆俵

俵俷倁丂俛丆俵

俵俷倁丂俢丆俵

俵俷倁丂俫丆俵

俫俴俿

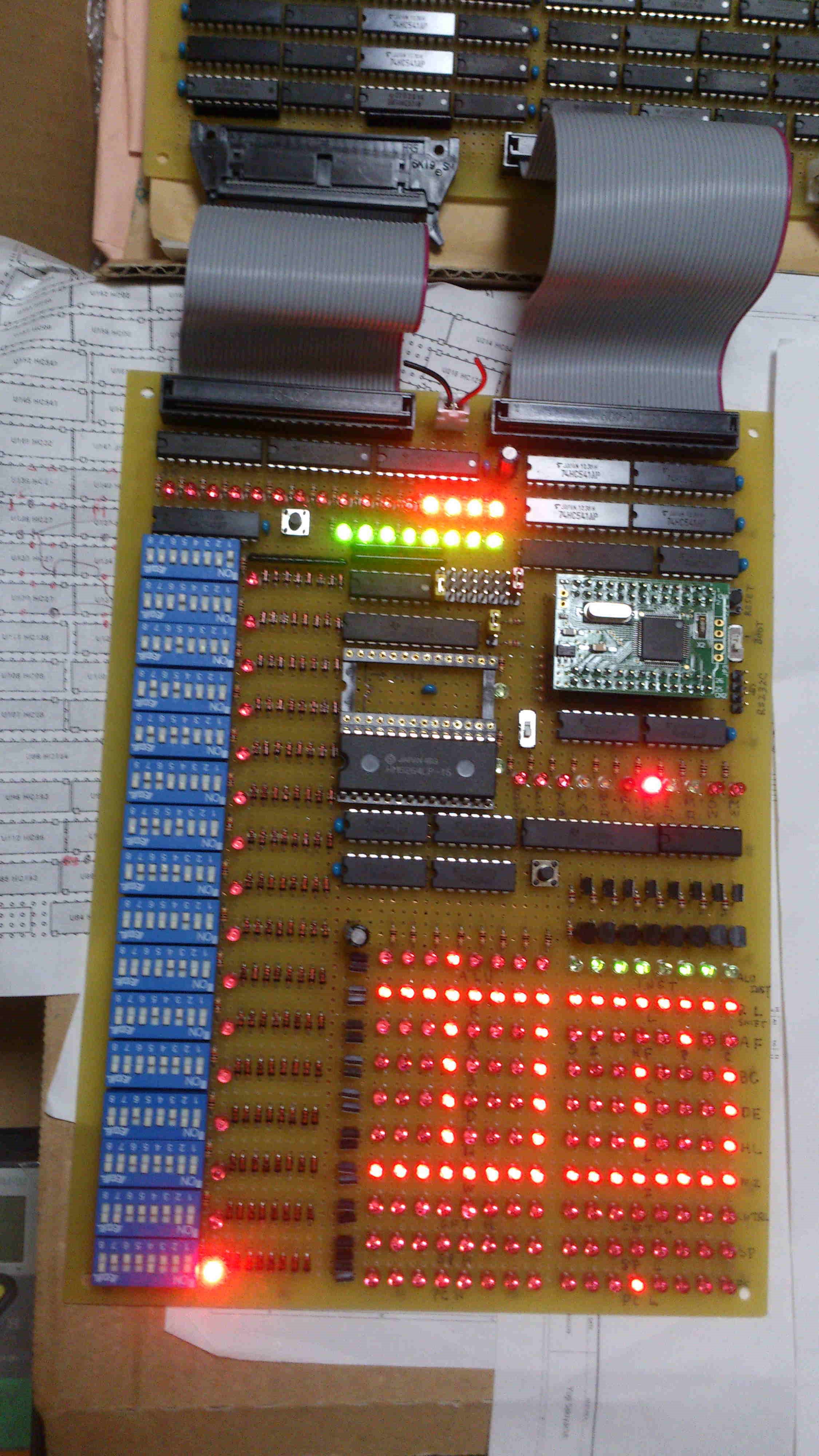

傪幚峴偟偨偲偒偺幨恀偱偁傞丅

俀侽侾俈擭俈寧拞夁偓

丂俬俶俼丄俢俠俼柦椷偑弌棃偨丅憗懍僥僗僩偟偰傒傞丅

傑偢偼俬俶俼偐傜丅

俴倃俬丂俛丆侾侽侾侽俫

俵俷倁丂俢丆俠

俵俷倁丂俤丆俠

俵俷倁丂俫丆俠

俵俷倁丂俴丆俠

俵俷倁丂俙丆俠

俬俶俼丂俛

俬俶俼丂俠

俬俶俼丂俢

俬俶俼丂俤

俬俶俼丂俫

俬俶俼丂俴

俬俶俼丂俙

俫俴俿

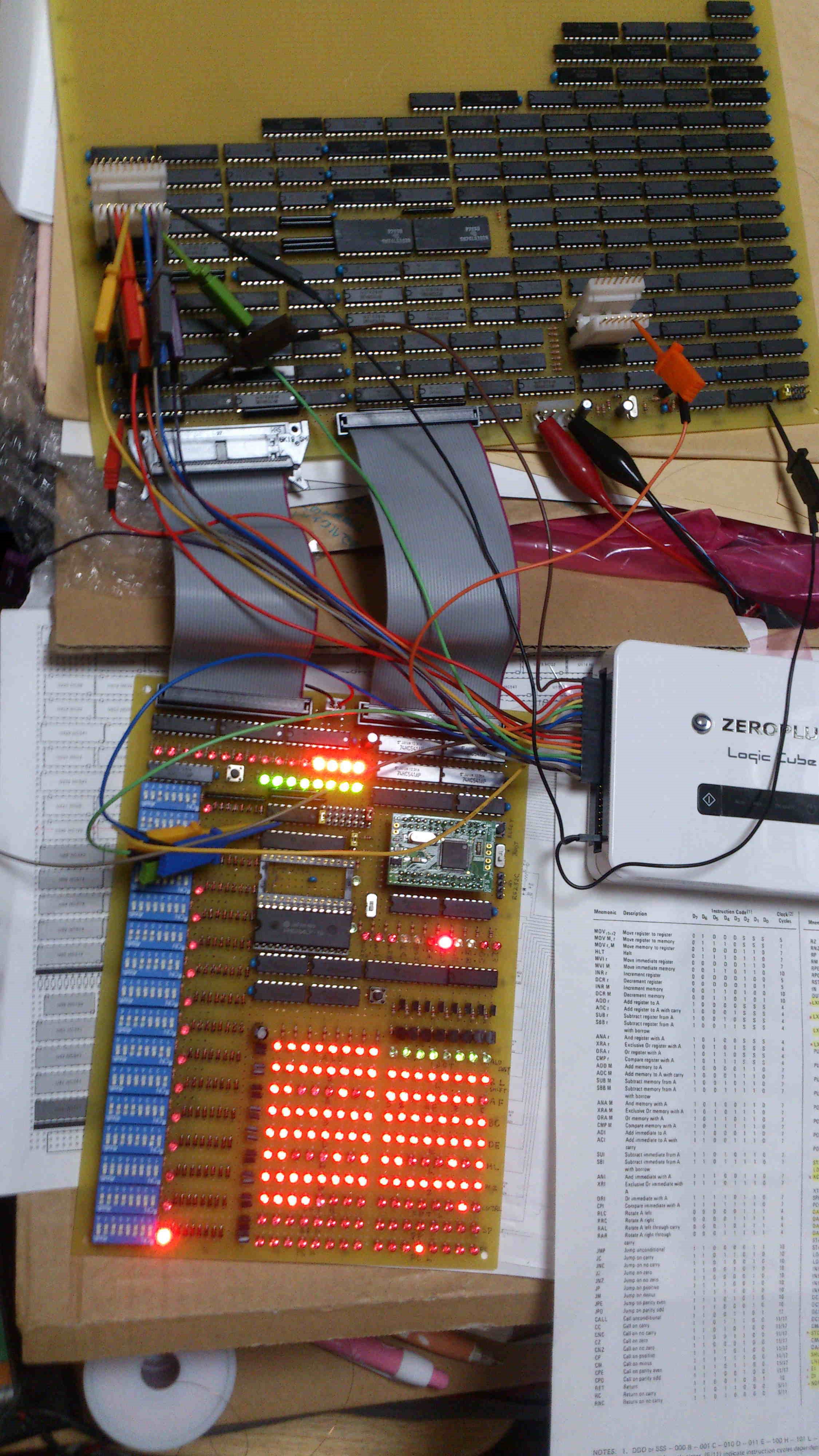

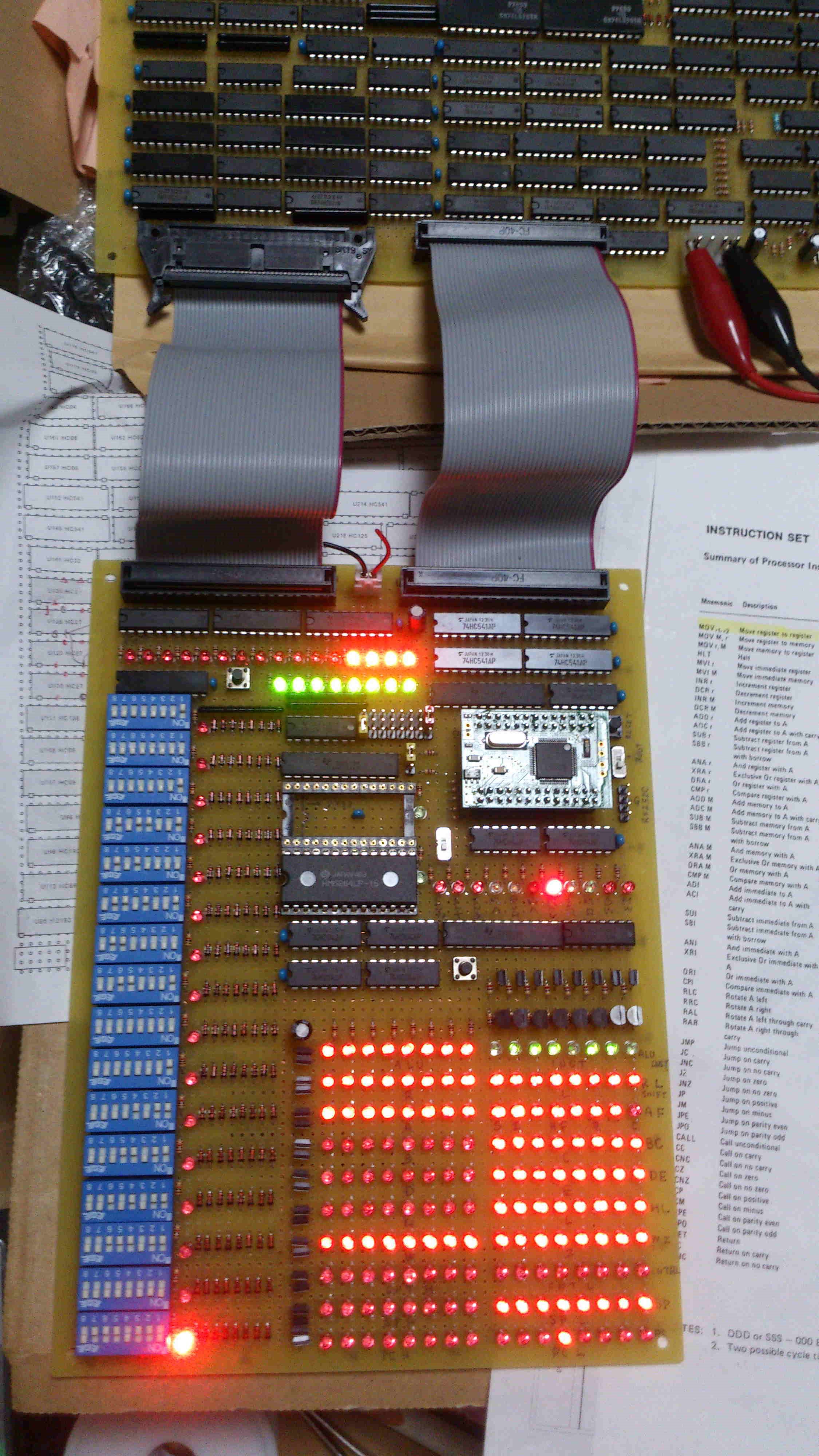

僥僗僩偟偨幨恀丅儗僕僗僞偑侾侾俫偲側偭偰偄傞丅傛偟傛偟丅

偱偼丄師偼俢俠俼偩丅俬俶俼傪俢俠俼偵曄偊偰幚峴丅偆傑偔偱偒偨丅

師偵壗婥偵俢俠俼傪俴偩偗偵偟偰傒偨丅丒丒丒丒両丒丒丒丒偍傗乣丄俙儗僕僗僞偵傕摨偠抣偑擖傞丅丠丠丠丅偠傖偀丄俫儗僕僗僞偩偲丒丒丒丒丅傗偭傁傝摨偠偩丄俙儗僕僗僞偵摨偠抣偑擖傞丠丠丠丠丅

偱偼丄偲尵偆偙偲偱儘僕僢僋傾僫儔僀僓偩丅偊偭両儘僕僢僋傾僫儔僀僓傪宷偖偲偆傑偔摦嶌偡傞丅俙儗僕僗僞偵偼奿擺偝傟側偄丅丒丒丒丠丠丠丒丒丒丅

俢俠俼幚峴晹偼俬俶俼幚峴晹偲摨堦偵側偭偰偄傞丅偮傑傝俬俶俼偲俢俠俼傪俷俼偟偰柦椷幚峴晹偵俤俶俙俛俴俤傪弌偡丅側偺偵俬俶俼偱偼栤戣柍偄丅俢俠俼幚峴偵怣崋偑弌側偄丠偄傗偄傗幚峴偼偟偰偄傞偺偩偐傜栤戣柍偄偼偢丅偙偺怣崋偩偗儘僕僢僋傾僫儔僀僓偵愙懕偟偰儌僯僞偟傛偆偲偡傞偲尰徾偑弌側偔側傞丅偍傗乣丒丒丒丒丅暘偐傜傫丅帋偟偵揹埑傪應傞偲係丏俆倁偩丅栤戣柍偄丅俤俶俙俛俴俤帪偼俴儗儀儖乮傎傏侽倁乯偵側傞偼偢丅偪側傒偵懠偺柦椷偺抂巕偼係丏俋倁偩丅偆傫丒丒丒丅係丏俋倁丅偄傠偄傠應偭偨偑慡偰係丏俋倁偩丅偱偼俢俠俼偺偲偙傠偼壗屘偵係丏俆側偺偐丠偆乣乣傫丅柊偄丅崱擔偼怮傛偆丅

偝偰丄梻挬栚偑妎傔偨偲偨傫慚偄偨丅偒偭偲怮偰偄傞娫偵擼偑彑庤偵峫偊偰偄偨偺偐傕丅偦傟偼丄倁俠俠偑晜偄偰偄傞偺偱偼丄偲尵偆偙偲丅憗懍僥僗僞乕偱摉偨偭偰傒傞偲丄價儞僑両丅倁俠俠偑晜偄偰偄偨丅偦偙偐傜倁俠俠傪愙懕偟偰偄傞俬俶俼丆俢俠俼幚峴晹傕摴楢傟偵倁俠俠偑晜偄偰偄偨丅弌椡偺婑惗僟僀僆乕僪傑偨偼擖椡曐岇僟僀僆乕僪傪捠偠偰揹埑偑妡偐偭偰偄偨偺偩丅偱傕俠俵俷俽側偺偱摦嶌偟偰偟傑偆丅

倁俠俠傪僠僃僢僋偟偰栤戣晹傪廋惓偟偨丅

偱偼丄偳偆偩丅丒丒丒丒偁傝傖傝傖丅僟儊偱偁傞丅俙儗僕僗僞偺儔僢僠怣崋傪儘僕僢僋傾僫儔僀僓偱儌僯僞偡傞偲丄俢俠俼柦椷帪偵俙儗僕僗僞儔僢僠怣崋偵嵶偄僷儖僗偑弌偰偄傞丅俢俠俼偺懳徾儗僕僗僞偵偐偐傢傜偢丄偄偮傕弌傞丅壗屘偩偀乕乕丅丂丂丂偦偆偩丄堦斢怮偰傒傛偆丒丒丒丒goodnight

梻挬丒丒丒側偵傕慚偐側偐偭偨丅丒丒丒偟傖偁側偄丄挷嵏偩丅俢俠俼夞楬偺俙儗僕僗僞儔僢僠怣崋傪偼偢偟偰乮晜偐偣偰乯丄儘僕僢僋傾僫儔僀僓偱娤應偡傞偲丄傗傗偭両棫攈側儔僢僠怣崋偑弌偰棃偨丅偮傑傝儔僢僠怣崋偑働儞僇偟偰偄偨偺偩丅

偱偼俢俠俼柦椷幚峴帪偵摨帪偵摦嶌偡傞柦椷偑偁傞偼偢丅夞楬傪捛偭偐偗傞偲丒丒丒丄偁偭偨両丅俠俵俙柦椷偑摦嶌偟偰偟傑偆丅側偤偵丒丒丒丄偁偭両偦偆偐丅嶐擭偺侾侾寧偵夞楬嵟廔抜奒偺尒捈偟偱俬俶俼丄俢俠俼柦椷傪曄峏偟偨偺傪巚偄弌偟偨丅尦偺夞楬偼亄侾丄亅侾僇僂儞僩夞楬偱亄侾亅侾偟偰偄偨偑丄偙傟偱偼僼儔僌偑曄壔偟側偄偺偱丄俙俴倀偱亄侾亅侾偡傞傛偆偵曄峏偟偨偺偩偭偨丅

俙俢俢柦椷偲俽倀俛柦椷傪巊偭偰傕椙偄偑丄偦傟偱偼僗僥僢僾悢偑懡偔側傞偺偱丄側偵偐曽朄偼柍偄偐偲俈係俫俠侾俉侾偺僨乕僞僔乕僩偲暿偵僎僢僩偟偨儘僕僢僋昞傪偵偵傜傫偱丄俽丄俵怣崋偲俠乮僉儍儕乕乯偺慻傒崌傢偣偱丄擖椡俙偺弌椡偑俙亄侾偺応崌偲俙亅侾偺応崌偑偁傞偙偲偑暘偐偭偨丅亄侾偡傞応崌偼尰忬偺夞楬乮捠忢俽丆俵偑慡偰俫儗儀儖乯偵俠亖侾乮俫儗儀儖乯偵偡傟偽俙亄侾偑弌椡偝傟傞丅側偺偱俬俶俠偺応崌偼俠傪俫偵偡傞俷俼夞楬傪捛壛偟偨丅亅侾偡傞応崌偼俽丆俵傪慡偰俴儗儀儖偵偡傟偽椙偄丅尰忬偺夞楬偱偼俠俵俙偲俙俢俢偺怣崋傪摨帪偵擖傟傞偲椙偄偺偱丄偦偺傛偆偵夞楬傪嶌惉偟偨偺偱偁傞丅

偱偼俙俢俢傕傑偢偄偺偐偲尵偆偲偙傟偼戝忎晇偱偁傞丅墘嶼柦椷乮俙俢俢丆俽倀俛側偳乯幚峴偵俙俢俢偡傞偐俽倀俛偡傞偐偺慖戰怣崋偲偟偰偄偰丄僩儔僀僗僥乕僩弌椡偲側偭偰偄偰働儞僇偟側偄丅俠俵俙偼扨撈偺柦椷幚峴巜椷側偺偱丄偙傟偵俢俠俼傪擖傟傞偲偙偺怣崋帺懱傕働儞僇偟偰偄傞偺偱偁傞丅

俠俵俙柦椷嶌惉帪偼俢俠俼柦椷晹偼枹幚憰偩偭偨偺偱丄摦嶌妋擣偱婥晅偐側偐偭偨偑丄傕偟俢俠俼柦椷傪愭偵嶌偭偰偄偨傜俠俵俙柦椷偱擸傫偱偄偨偐傕偟傟側偄丅

俙俴倀偵擖傟傞俠俵俙偺怣崋傪梋偭偨俷俼夞楬偱俠俵俙丄俢俠俼傪俷俼偟偰愙懕偟偨丅

偙傟偱傛偆傗偔俢俠俼柦椷偑姰帏偵摦嶌偟偨丅

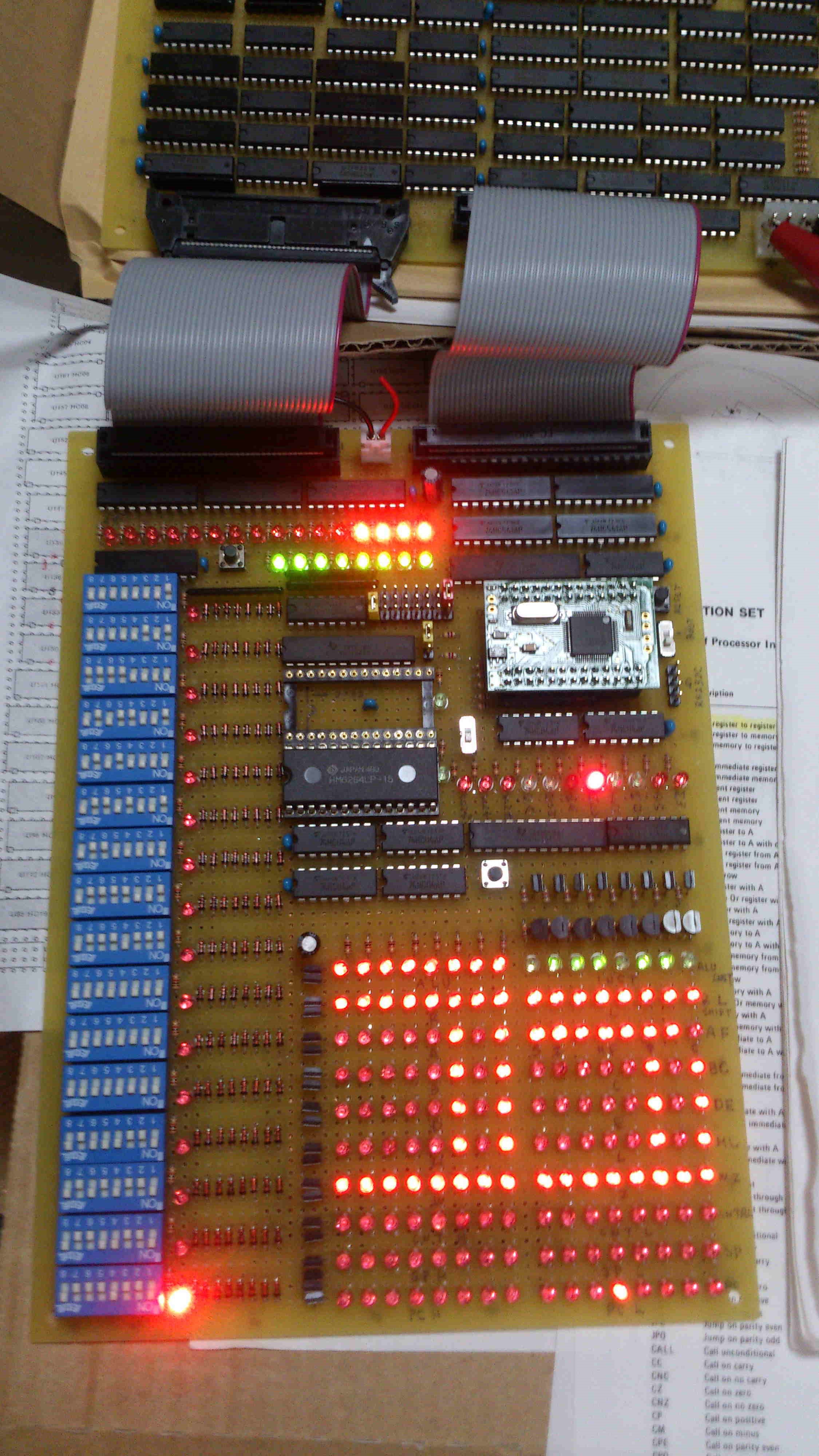

偮偄偱偵俠俵俙柦椷傕捛壛偟偰僥僗僩偟偨幨恀丅

俀侽侾俈擭俈寧枛

丂俼俼俠丄俼俙俼丄俼俴俠丄俼俙俴丄俬俶俼丂俵丄俢俠俼丂俵丄俠俵俠丄俵倁俬丂俵偑姰惉偟偨丅

憗懍僥僗僩偟偨丅崱搙偼偁偭偗側偔摦嶌偟偨丅僗儖僢偲摦嶌偟偰傕柺敀偔側偄偑丒丒丒丅偲傝偁偊偢摦嶌偟偨偺偱俷俲偲偟傛偆丅乮幨恀偼柍偟丅偁偭偰傕儔儞僾偑揰摂偟偰偄傞偩偗偱偮傑傜側偄丠丒丒丒乯

俀侽侾俈擭俉寧弶擔

丂俵倁俬丂倰丂偑偱偒偨丅憗懍僥僗僩偟偨丅

俵倁俬丂俛丆侾

俵倁俬丂俠丆俀

俵倁俬丂俢丆俁

俵倁俬丂俤丆係

俵倁俬丂俫丆俆

俵倁俬丂俴丆俇

俵倁俬丂俙丆俈

俫俴俿

偆傑偔摦嶌偟偨丅儔儞僾偑揰摂偟偰偄傞偩偗偩偗偳丄庘偟偄偺偱幨恀傪傾僢僾丅

俀侽侾俈擭俉寧拞

丂偍杶偺婣徣偱拞抐偟偰偄偨偑丄傛偆傗偔嵞奐偟偰柦椷傪嶌偭偨丅

俽俹俫俴丄俹俠俫俴偑傑偢偱偒偨丅

庢傝姼偊偢摦嶌偟偨偺偱丄俹俠俫俴傪巊偭偰侽斣抧傊栠傞傛偆偵偟偰儖乕僾偝偣偰丄挿帪娫儔儞僯儞僌偟偰傒偨丅摿偵栤戣側偔摦嶌偟偰偄傞丅

師偵嶌偭偨偺偼

俹俷俹丄俼俤俿偲俼倃倃乮忦審俼俤俿乯偱偁傞丅側偤偵愭偵俹俷俹偩偗偐偲尵偆偲丄夞楬恾偺弴斣偑偦偆側偭偰偟傑偭偨偩偗偺帠偩丄怺偄堄枴偼柍偄丅乮摉慠丠乯

儊儌儕乕偵僨乕僞傪彂偄偰偍偄偰俹俷俹偱庢傝弌偡僥僗僩傪幚峴丄栤戣側偔摦嶌偟偨丅

俼俤俿傕栠傝斣抧傪儊儌儕乕偵彂偄偰俼俤俿偱庢傝弌偡偲偦偙傊僕儍儞僾偡傞丅偙傟傕栠傝傪侽斣抧偵偟偰丄儖乕僾偝偣偰傒偨丅栤戣側偟丅

偝偰忦審俼俤俿偩偑丄忦審偑惉棫偟偰俼俤俿倀俼俶偡傞応崌偼栤戣柍偄偑丄忦審偑惉棫偟側偐偭偨偲偒偵師偺僗僥僢僾偵恑傓偼偢偺偲偙傠偑丄師偺師傊旘傫偱偟傑偆丅

儘僕僢僋傾僫儔僀僓偱妋擣偡傞偲丄忦審晄惉棫帪偺柦椷僋儕傾偑巚偭偨傛傝抶偔丄師偺柦椷偺傾僪儗僗儔僢僠偵娫偵崌偭偰側偄丅埲慜彂偄偨傛偆偵傾僪儗僗儔僢僠偼係僋儘僢僋栚偩偑丄偙傟偑嵟屻偺僋儘僢僋側偺偱丄偙傟埲忋抶傜偣傜傟側偄丅傕偲傕偲偺僞僀儈儞僌愝寁偑傑偢偄偺偱偁傞偑丄偙偙傑偱嶌偭偰偟傑偭偨傜抳偟曽側偄丅僋儘僢僋僇僂儞僩傕僋儕傾偡傞傛偆偵曄峏偡傞偟偐側偄丅偙偆偡傞偲丄柦椷幚峴帪娫偺尒愊傕傝偑擄偟偔側傞偑丄摦嶌偟側偄傛傝偼傑偟丄偲尵偆偙偲偱夵憿偟偨丅側偺偱柦椷幚峴帪娫偼儅僔儞僒僀僋儖偺帪娫亄傾儖僼傽乮柦椷儕僙僢僩偺抶傟乯偲側偭偰偟傑偭偨丅

傕偟惢嶌搑拞偱偆傑偄曽朄傪峫偊晅偄偨傜夵憿偡傞偐傕偟傟側偄丅

俀侽侾俈擭俉寧拞

丂堷偒懕偒丄俹倀俽俫柦椷傪幚憰偟偨丅

偱偼丄僥僗僩偩丅

俴倃俬丂俛丆侽俙俙俆俆俫

俹倀俽俫丂俛

俹俷俹丂丂俢

俹倀俽俫丂俢

俹俷俹丂丂俫

俹倀俽俫丂俫

俹俷俹丂丂俹俽倂

俫俴俿

偝乕乕偁丄偳偆偩丅丒丒丒丒偍傗偭丠丄偆傑偔峴偐側偄偧丅丒丒丒丒

偁偭両丄傑偢偄偠傖傫両丅

俴倃俬丂俽俹丆侽俥侽侽侽俫

俴倃俬丂俛丆侽俙俙俆俆俫

俹倀俽俫丂俛

俹俷俹丂丂俢

俹倀俽俫丂俢

俹俷俹丂丂俫

俹倀俽俫丂俫

俹俷俹丂丂俹俽倂

俫俴俿

偦偆丄僗僞僢僋億僀儞僞傪愝掕偟側偗傟偽丅

偝偁丄偳偆偩丅丒丒丒丒傗偭傁傝偆傑偔峴偐側偄丅

傗傟傗傟丄儘僕僢僋傾僫儔僀僓偺弌斣偩丅

偳傟偳傟丄偍傗乣丅僗僞僢僋億僀儞僞傪亅侾偡傞丄嵟弶偺怣崋偑弌偰偙側偄丅柦椷幚峴僞僀儈儞僌偺儅僔儞僋儘僢僋侾僋儘僢僋栚偱亅侾偡傞怣崋傪嶌偭偰偄傞偑丄柦椷幚峴晹偺僩儔僀僗僥乕僩弌椡偺俤俶俙俛俴俤傕摨僞僀儈儞僌偱擖傞丅埲慜俵侾偱柦椷僨僐乕僟傪僽儘僢僋偡傞傛偆偵夵憿偟偨偺偱丄俵侾夝彍偱柦椷弌椡怣崋偑弌偰丄偦傟傪俫俠侽係偱斀揮偝偣偰俤俶俙俛俴俤怣崋偲偟偰偄傞偺偱丄幚嵺偵亅侾怣崋偑弌椡偵尰傟傞偺偑抶傟偰弌偰偙側偄丅俤俶俙俛俴俤偱僩儔僀僗僥乕僩偑桳岠側偭偨偲偒偼俀僋儘僢僋栚偵側偭偰偄傞偺偩丅偙傟偱偼偳偆偁偑偄偰傕亅侾怣崋偑弌偰偙側偄丅偦偙偱巇曽側偔丄亅侾怣崋偼俀僋儘僢僋栚傪巊偆偙偲偵偟偨丅偨偩偟丄偙偆偡傞偲傾僪儗僗儔僢僠傪俁僋儘僢僋栚偵偟偰偄傞偺偱丄僗僞僢僋傪亅侾偟偨寢壥偑傾僪儗僗儔僢僠偵娫偵崌傢側偄丅

埬偢傞傛傝嶻傓偑傗偡偟偱幚嵺偵摦嶌偝偣傞偲丄偆傑偔摦嶌偟偨丅偄偄偺偐側偁乣丅僗僞僢僋偺僇僂儞僩姰椆偐傜傾僪儗僗儔僢僠傑偱偺帪娫傪儘僕僢僋傾僫儔僀僓偱尒偰傒傞偲丄侾侽乣俀侽値倱偵側偭偰偄傞丅

偪傚偭偲偒傢偳偄偺偱丄傾僪儗僗儔僢僠怣崋傪侾抜僶僢僼傽傪捠偟偰抶傜偣偰傒偨丅偙傟偱愭偺帪娫偼俀侽乣俁侽値倱偲側偭偨丅

庢傝姼偊偢偙傟偱偟偽傜偔條巕傪尒傛偆丅

俀侽侾俈擭俉寧枛

丂師偵偱偒偨偺偼丄俠俙俴俴丄俠倃倃乮忦審僐乕儖乯偲俷倀俿柦椷偩丅

憗懍俠俙俴俴傪僥僗僩偟偨偑偆傑偔峴偐側偄丅傗偭傁傝僗僞僢僋偺偲偙傠偩傠偆偲摉偨傝傪晅偗偰儘僕僢僋傾僫儔僀僓偱尒偰傒傞偲丄傗偭傁傝偦偆偱偁偭偨丅偙偺夞楬偱偼傾僪儗僗儔僢僠偑僗僞僢僋偺亅侾僇僂儞僩姰椆傛傝傢偢偐偵憗偄丅俹倀俽俫傒偨偄偵僎乕僩傪擖傟偰傕僊儕僊儕偩偐傜偙偺庤傕巊偊側偄丅偟偽傜偔擸傫偩偑丄儔僢僠怣崋傪斀揮偝偣傛偆丅偮傑傝僀儞僶乕僞乮俫俠侽係乯偱斀揮偝偣傞偲儔僢僠偺棫偪忋偑傝僄僢僕偑俇俀丏俆値倱抶偔側傞丅僎乕僩偺怣崋偑柦椷偺俤俶俙俛俴俤偱弌偨偲偨傫侾夞儔僢僠偝傟偰偟傑偆偑丄偦偺捈屻惓偟偄僨乕僞乮傾僪儗僗乯偑儔僢僠偝傟傞丅

帋偟偵傗偭偰傒傞偲偆傑偔摦嶌偟偨丅傒偭偲傕側偄曽朄丄幾摴偐傕偟傟側偄偑帺暘偱巊偆儅僀僐儞側偺偱椙偟偲偟傛偆丅弌棃偨嬇偵偼夞楬恾傪傾僢僾偟傛偆偲巚偭偰偄偨偑丄撍偭崬傒偳偙傠枮嵹偺夞楬偵側偭偰偟傑偭偨偺偱丄巭傔傞偙偲偵偟傛偆乮儎儗儎儗乯丅

偲偙傠偱俷倀俿柦椷偼俬俶丄俷倀俿偺僥僗僩夞楬傪搵嵹偡傞偺傪朰傟偰偄偨偺偱僥僗僩偱偒側偄丅俬俷俼俤俙俢丄倂俼俬俿俤怣崋偑弌偰偄傞偺傪妋擣偟偨偩偗偩丅

働乕僗偵廂傔偨帪偺僷僱儖偺夞楬偱俬俷傪巊偭偰偄傞偺偱偦偺帪偺偍妝偟傒偩丅

俀侽侾俈擭俉寧枛

丂師偵俬俶丄倃俿俫俴偲俼俽俿嶌惉丅偙傟偱嵟屻偩丅

偝偰丄倃俿俫俴偺妋擣丅幚峴偲摨帪偵偳偙偐傊偡偭旘傫偩丅偍傗乣丄儘僕僢僋傾僫儔僀僓偩丅偱傕傛偔暘偐傜傫丅嵞搙夞楬傪妋擣丅偁偭両丄偟傑偭偨丅倃俿俫俴偼僗僞僢僋偐傜僨乕僞傪庢傝弌偟偰倂倅儗僕僗僞傊戅旔偟偰丄俫俴儗僕僗僞傪僗僞僢僋偵彂偄偰丄倂倅儗僕僗僞傪俫俴傊彂偔摦嶌偩偑丄倂倅儗僕僗僞傊偺傾僋僙僗偼俠俙俴俴偱傕巊偭偰偄傞丅俠俙俴俴偺応崌偼柦椷偵懕偔旘傃愭傾僪儗僗傪倂倅儗僕僗僞傊擖傟偰偍偒丄俹俠乮僾儘僌儔儉僇僂儞僞乯傪僗僞僢僋傊擖傟偰丄俹俠傊倂倅儗僕僗僞偺僨乕僞傪彂偔偲旘傃愭傊幚峴偑堏傞丅偙偺倂倅儗僕僗僞偺晹暘傪僐僺乕偟偰偦偺傑傑偩偭偨偺偩丅偮傑傝僗僞僢僋傊擖傟偨揔摉側僨乕僞傪俹俠傊僙僢僩偟偰偟傑偭偰偄偨丅乮傗傟傗傟乯丅憗懍廋惓丅倂倅儗僕僗僞傪俫俴儗僕僗僞傊彂偔傛偆偵曄峏丅柍帠摦嶌偟偨丅

丂師偵俼俽俿柦椷偩丅屌掕乮俉偲偍傝乯偺僒僽儖乕僠儞僐乕儖偲摨偠偱偁傞丅傑偢僗僞僢僋偵俹俠傪戅旔丄俼俽俿柦椷偵傛傞旘傃愭傪俹俠傊僙僢僩偡傞丅傑偢僗僞僢僋偵戅旔偡傞偺偱丄俹倀俽俫柦椷偲摨偠僞僀儈儞僌傪棳梡偟偰嶌惉丅栤戣側偔摦嶌偟偨丅

俠俙俴俴偲摨偠偵偟側偗傟偽側傜側偄偐偲傕巚偭偨偑丄俹倀俽俫偲摨偠僞僀儈儞僌偱戝忎晇偩偭偨丅

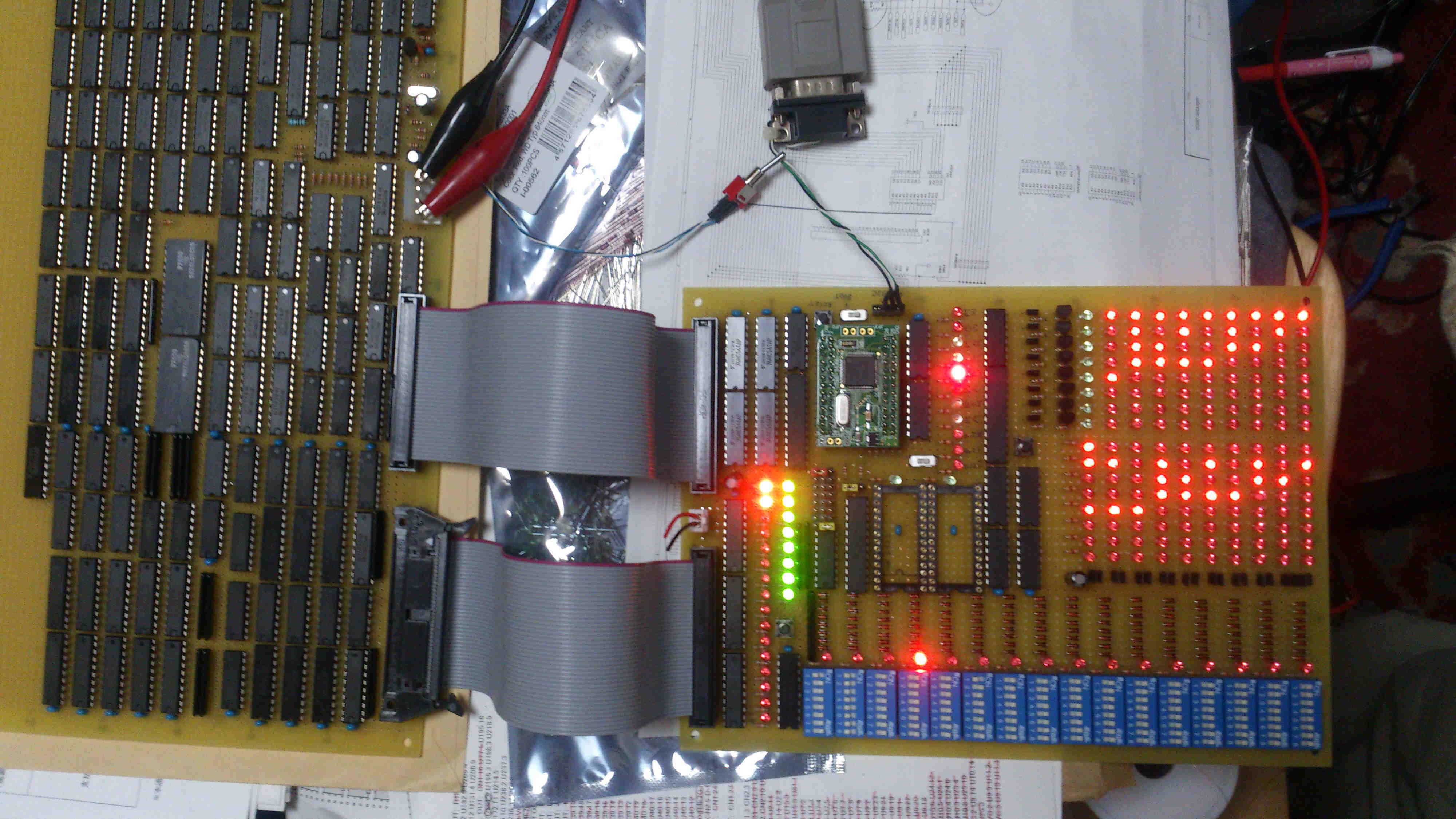

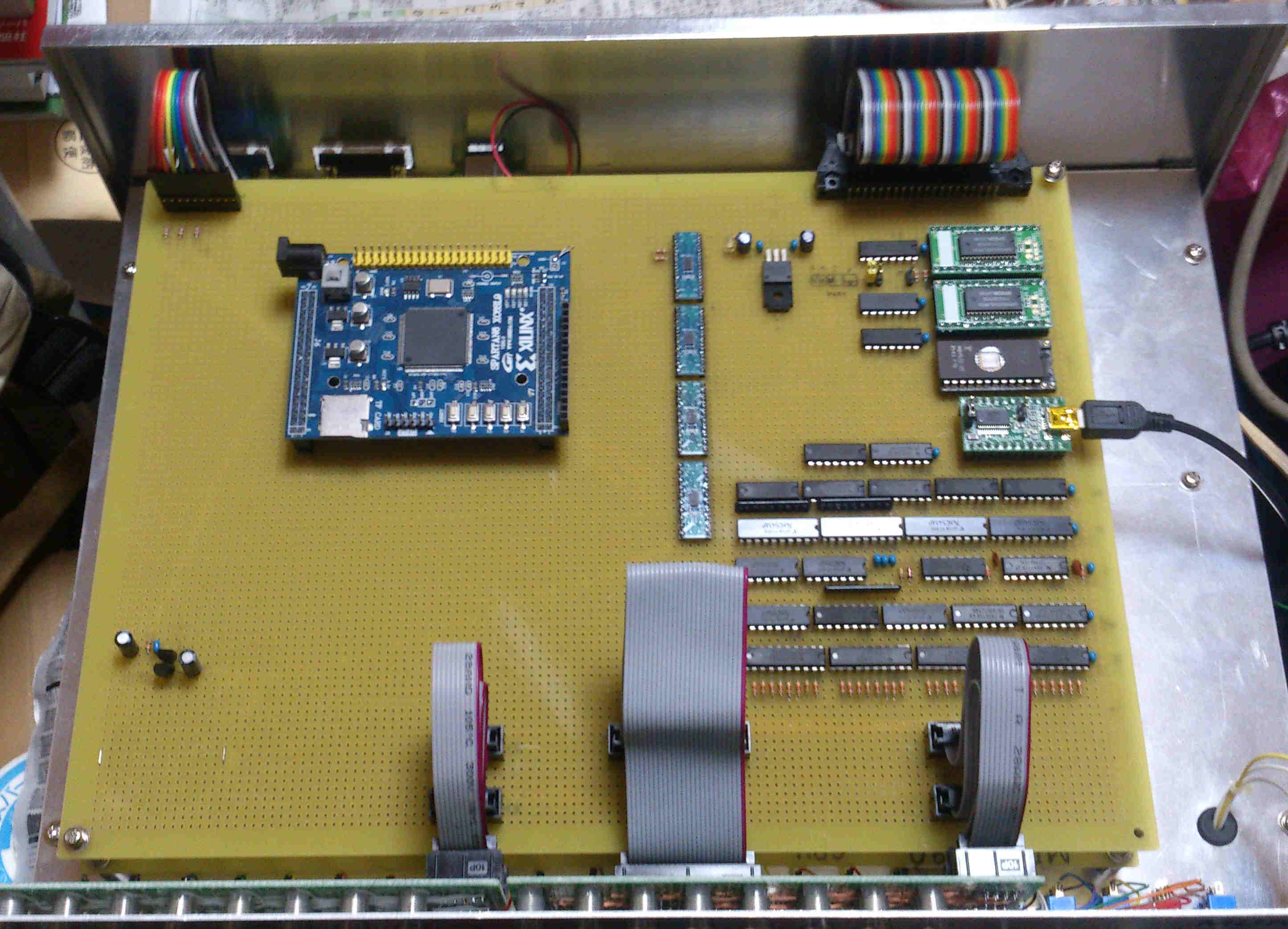

俀侽侾俈擭俋寧弶

丂偝偰丄庢傝姼偊偢柦椷偑姰惉偟偨丅偍傛偦俀侾侽擔妡偐偭偨偺偱丄傗偭傁傝俀侽杮乛擔偺儁乕僗偩偭偨偙偲偵側傞丅

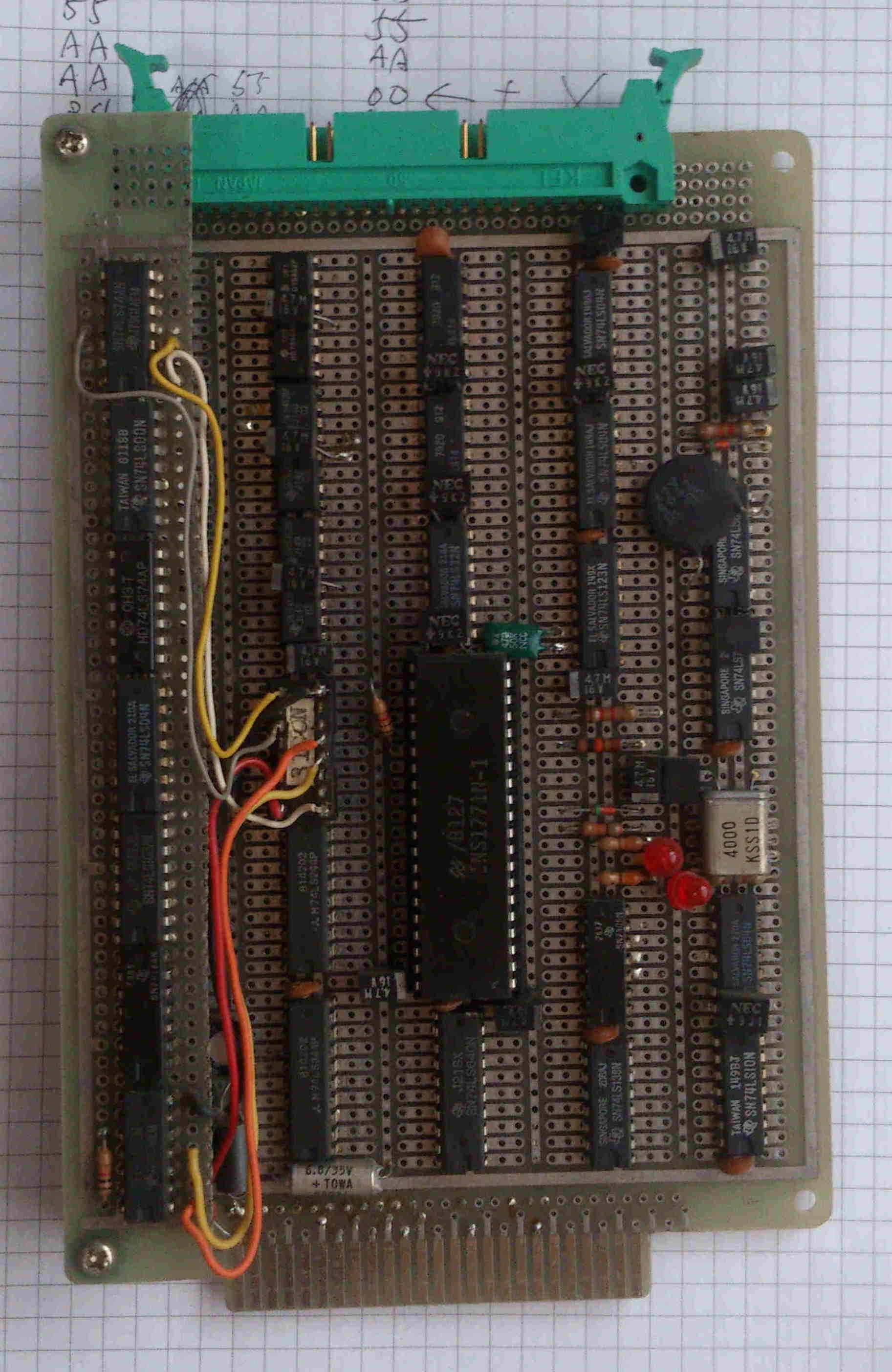

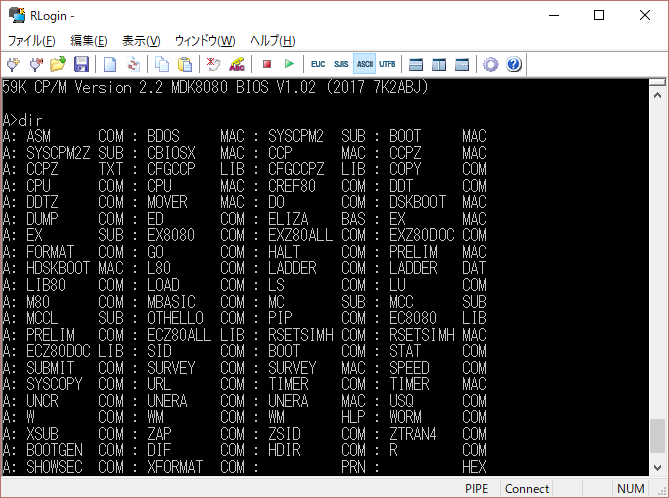

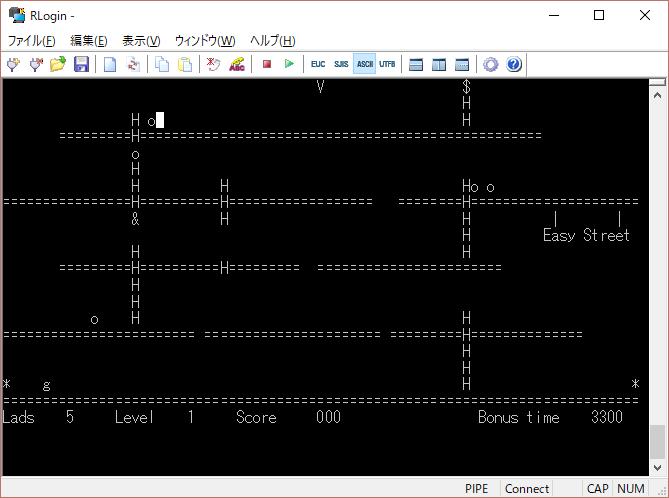

偱偼丄楢懕柦椷僥僗僩傪傗偭偰傒傛偆丅俢俬俹俽倂偺俼俷俵偱偼僗僥僢僾偑晄懌側偺偱杮暔偺俼俷俵偵搊応偟偰傕傜偍偆丅

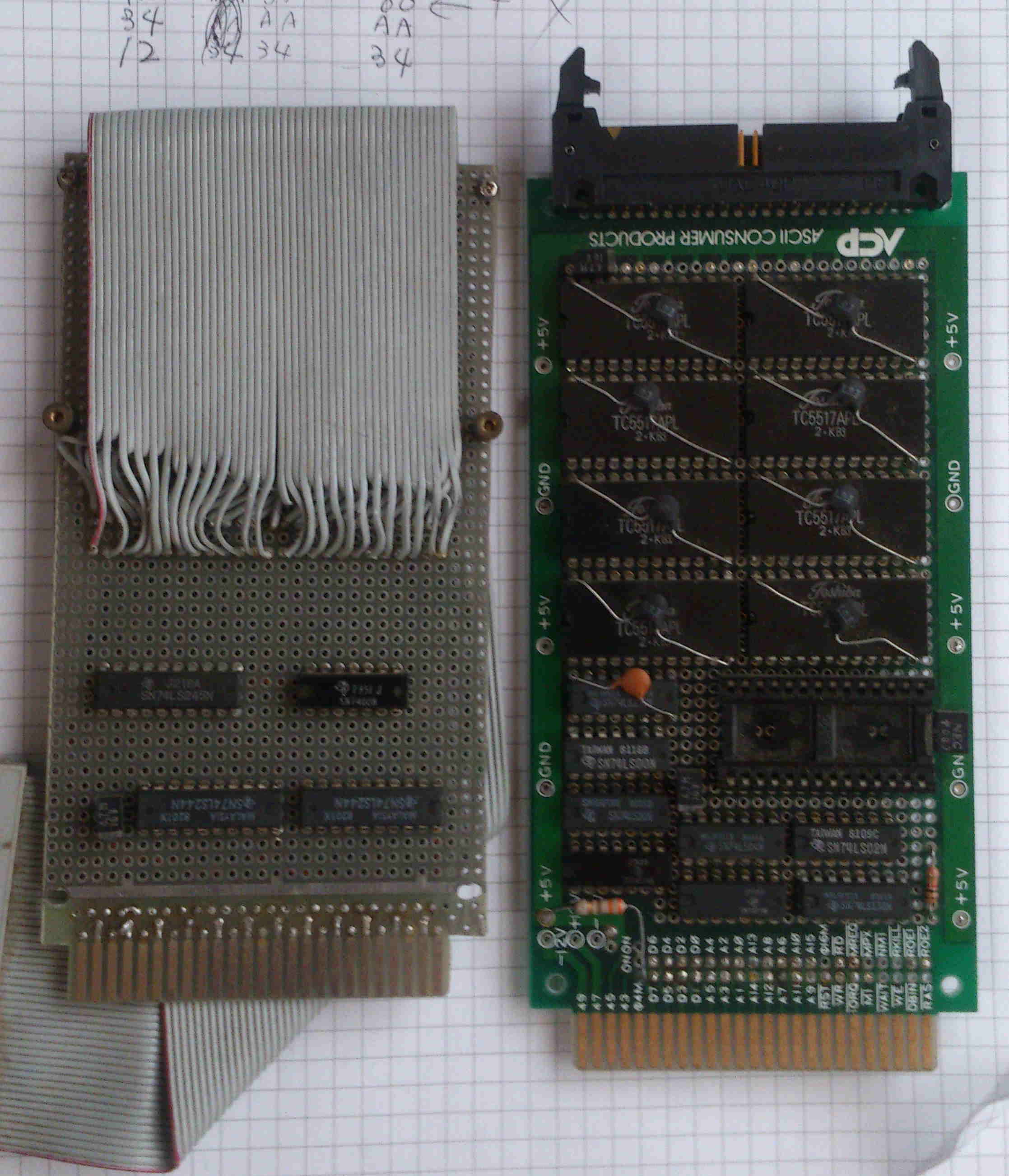

俼俷俵偵彂偔僥僗僩僾儘僌儔儉偼偁傜偐偠傔僟僂儞儘乕僪偟偨altair8800_emulater傪巊偭偰CP/M傪摦嶌偝偣丄CP/M忋偱摦嶌偡傞俉侽俉侽柦椷僥僗僩僾儘僌儔儉傪丄偙偺DEBUG儃乕僪梡偵廋惓偟偰僐儞僷僀儖偟偨丅弌棃忋偑偭偨儕僗僩偲HEX僼傽僀儖傪WIN傊揮憲偟偰丄HEX僼傽僀儖傪僞乕儈僫儖僜僼僩偱PROM儔僀僞乕傊揮憲偟偰ROM傪從偄偨丅

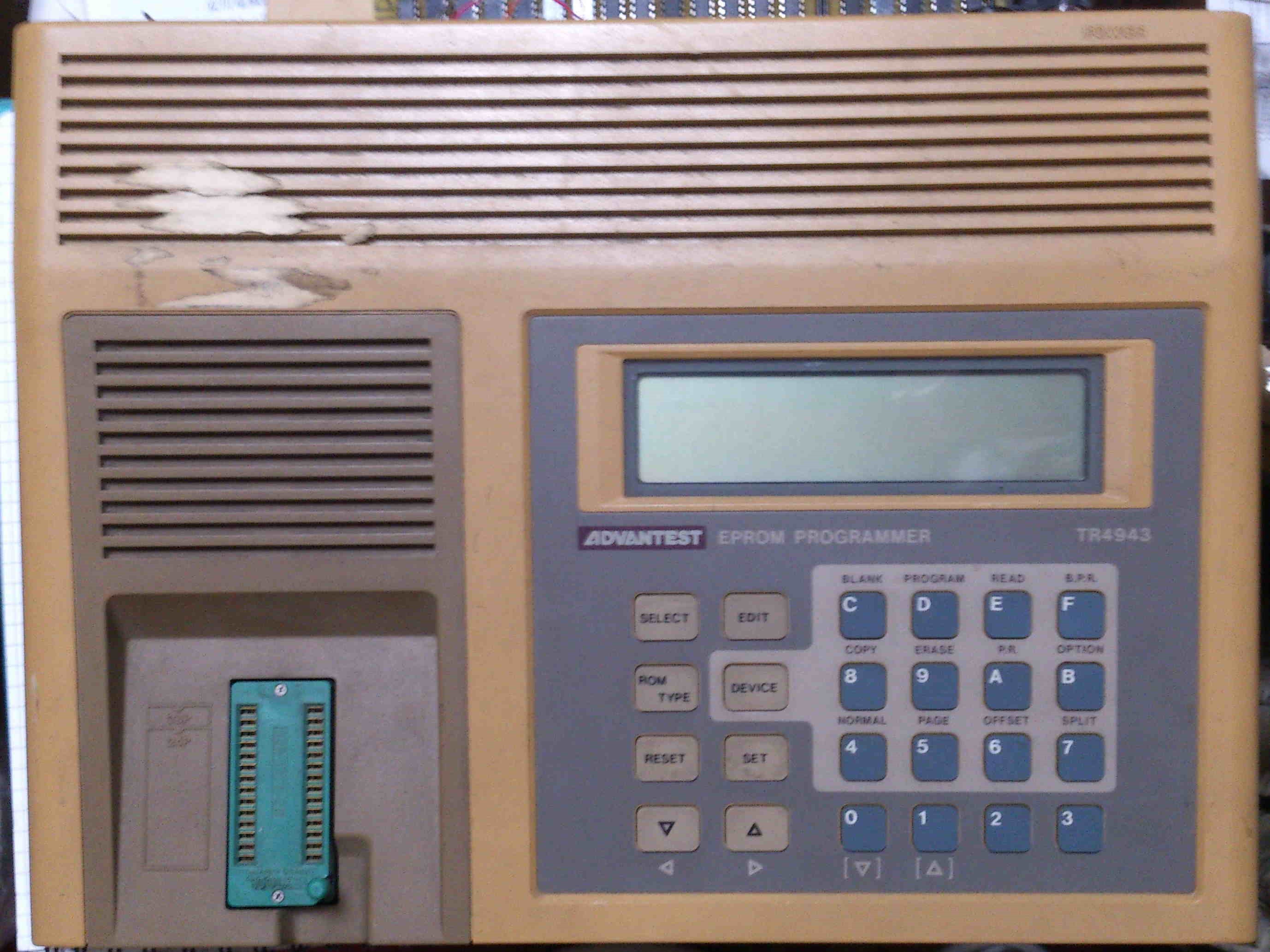

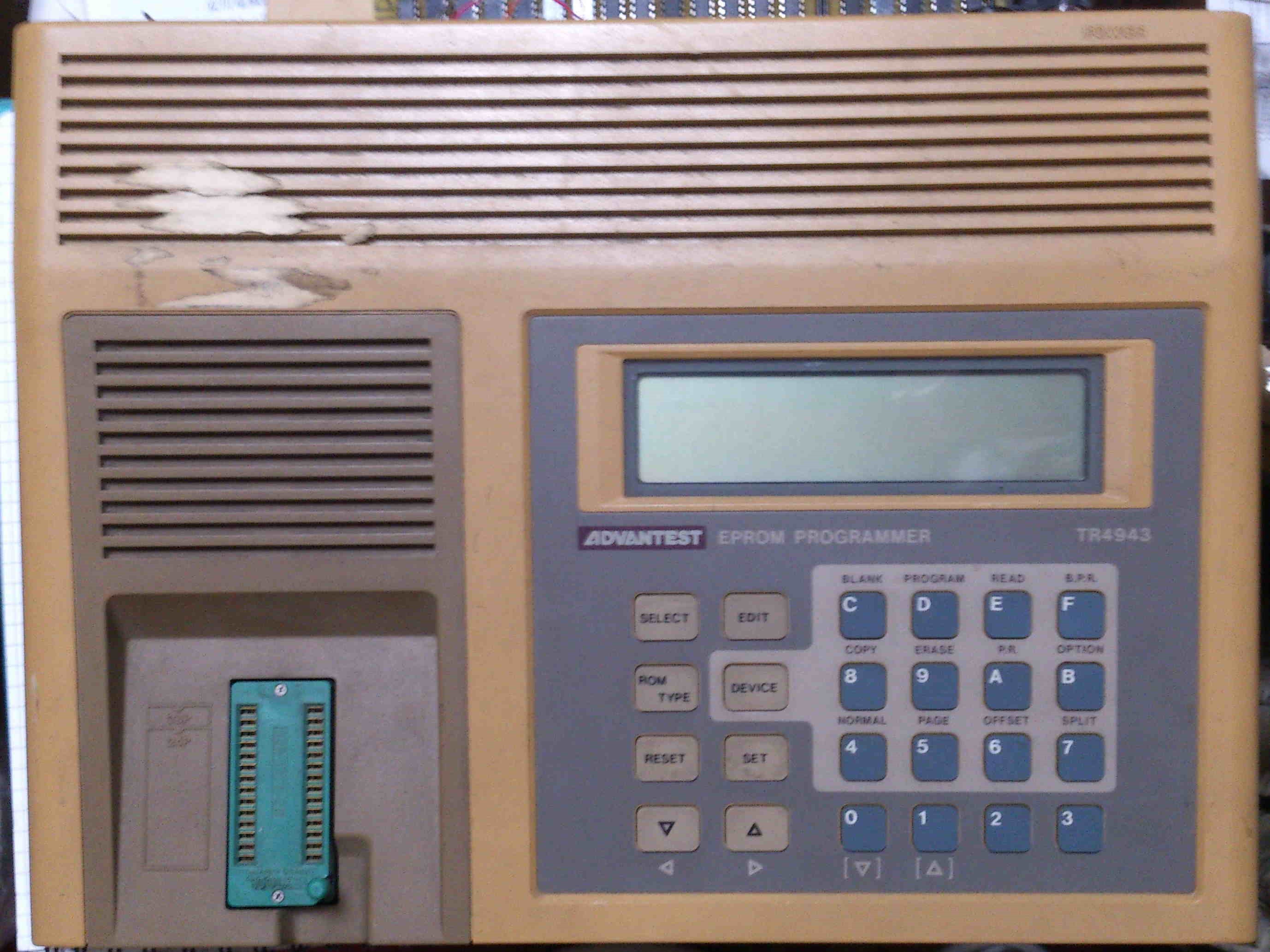

PROM儔僀僞乕偼墴擖傟偐傜敪孈偟偰偒偨丅摨帪偵PROM傕敪孈丅PROM偼偄傠偄傠偁偭偨偑MB8532傪巊梡丄係倠僶僀僩偺PROM偩丅偦傫側偵梕検偼偄傜側偄偑偙傟偑嵟彫梕検偺PROM偩偭偨丅

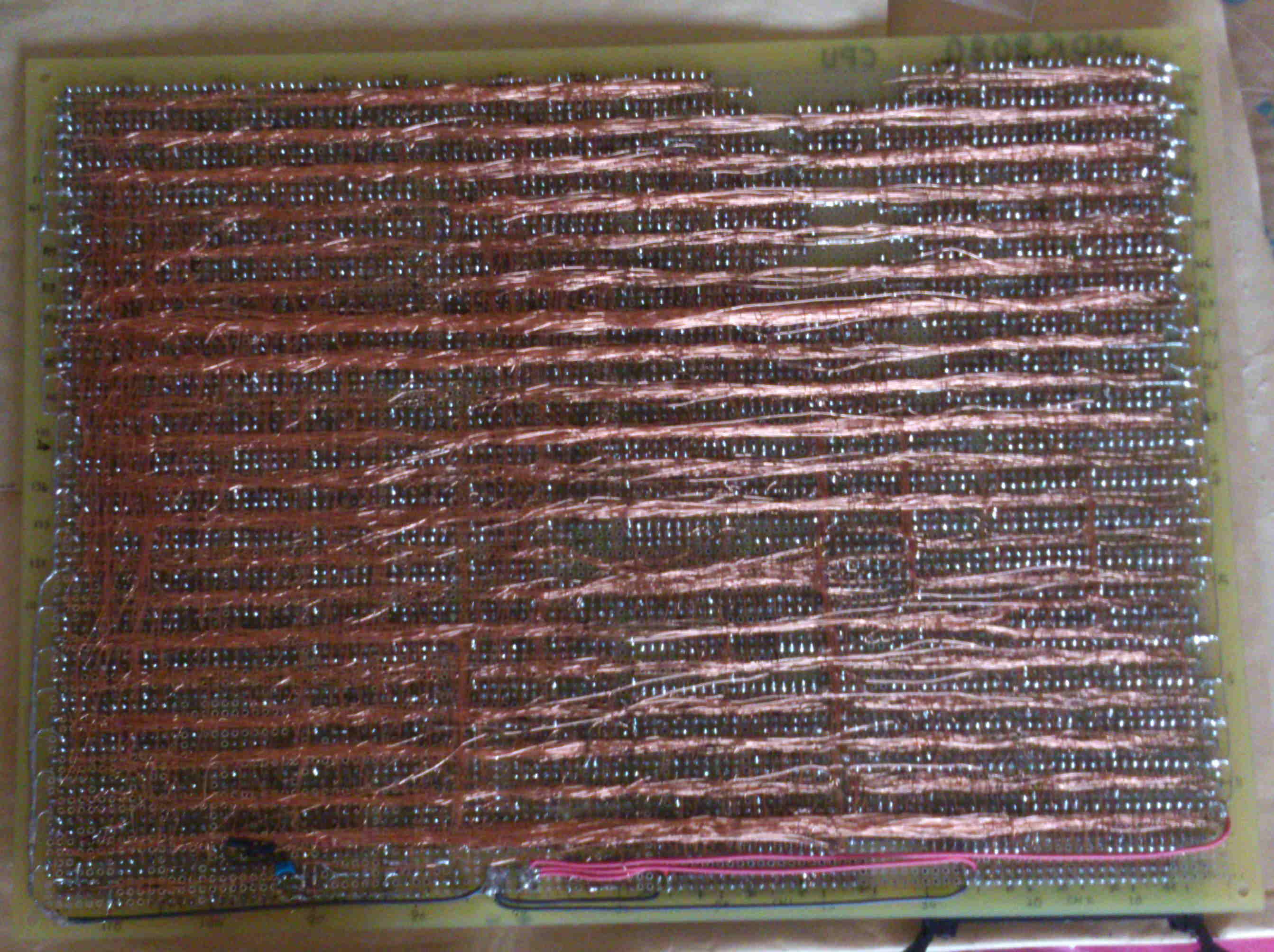

敪孈偟偨PROM儔僀僞乕

傕偆壗擭傕揹尮擖傟偰側偄偺偱丄嫲傞嫲傞揹尮擖傟偨傜丄僙儖僼僠僃僢僋偟偰OK偲弌偨丅堦埨怱丅

巊偄曽傪朰傟偰偟傑偭偨偺偱丄ADVANTEST偐傜儅僯儏傾儖傪僟僂儞儘乕僪乮曋棙偵側偭偨乯丅

RS232C偺僐僱僋僞偑俀俆PIN僐僱僋僞偩丅崱帪尒側偄僐僱僋僞偱偁傞丅偨偟偐偳偙偐偵俀俆僺儞亅俋僺儞曄姺僐僱僋僞偑偁偭偨偼偢偩偑丒丒丒丅傕偆壗擭傕巊偭偰側偄偟丒丒丒丄墴擖傟傪扵偟偨偑敪孈偱偒側偐偭偨丅巇條偑側偄偺偱丄偲傝偁偊偢俋僺儞偺儊僗僐僱僋僞傪偮偐偭偰曄姺傪嶌偭偨丅偲尵偭偰傕俀俆僺儞偑柍偄偺偱偙偪傜懁偼儕乕僪傪僐僱僋僞偺僜働僢僩偵捈愙嵎偟崬傫偱傒偨丅

儅僯儏傾儖傪尒側偑傜HEX僼傽僀儖傪揮憲偡傞偲偆傑偔揮憲偱偒偨丅INTEL偺HEX僼傽僀儖偵傕懳墳偟偰偄傞偺偱娙扨偱偁偭偨丅摉帪偺PROM儔僀僞乕偼怓傫側HEX僼傽僀儖偵懳墳偟偰偄傞丅

PROM偵彂偒崬傫偱DEBUG儃乕僪偵憰拝偟偨丅

丂偝偁丄幚峴偩丅

捈偖偵偢偭偙偗偨丅偁傝傖両丅僄儔乕偺応崌偼HL儗僕僗僞偵僄儔乕敪惗応強偺傾僪儗僗偑擖傞傛偆偵偟偰偄傞偺偱丄儕僗僩偱妋擣偡傞偲丅傫丄僉儍儕乕僼儔僌偑ON偟偰偄側偄妋擣偱僄儔乕偵側偭偰偄傞丅妋偐偵僉儍儕乕偑ON偟偰偄傞丅偙傟偼LOGIC墘嶼乮AND,OR,XOR乯偱僉儍儕乕偑OFF偟偰偄傞偙偲偺僥僗僩偱僄儔乕偵側偭偰偄傞丅

偁傝傖乣丅LOGIC墘嶼偱僉儍儕乕OFF丠丠丅俉侽俉侽偺儅僯儏傾儖傪尒傞偲丄妋偐偵僉儍儕乕偼儕僙僢僩偝傟傞偲彂偄偰偁傞丅夞楬偺嶌傝朰傟丠丅偆乣傫丅婰壇偺偐側偨偵偆偭偡傜偲丒丒丒丅

偦偆偩丄ALU偑傛傠偟偔傗偭偰偔傟傞偲巚偄偦偺屻慡偔婥偵偟偰偄側偐偭偨丅ALU偺A=B偺僥僗僩偱傗偭偰偍偗偽椙偐偭偨偺偩偑丄偦偺帪偼偡偭偐傝婰壇偺偐側偨偱偁偭偨丅

梋偭偨僎乕僩偱側傫偲偐弌棃偦偆偩丅憗懍捛壛偟偰摦嶌妋擣乮DIPSW偺僾儘僌儔儉乯OK偱偁傞丅

屻擔捛婰

傛偔峫偊偨傜丄俙俠偼乮僴乕僼僉儍儕乕偲傕尵偭偰偄傞乯偼偳偆側偺偩傠偆丅俙俴倀偼係價僢僩偱俀抜愙懕偟偰偄傞丅壓係價僢僩偺僉儍儕乕傪忋係價僢僩偵偄傟偰丄偙傟傪俙俠偲偟偰偄傞丅偮傑傝榑棟墘嶼偱俠偑俷俶偡傞側傜俙俠傕俷俶偡傞偼偢偱偁傞丅帋偡偲傗偼傝俙俠偑俷俶偟偰偄傞丅偦偙偱媈栤丅俢俙俙柦椷偺僥僗僩偱俙俠傪僋儕傾偡傞偨傔偵俷俼柦椷傪幚峴偟偰偄傞丅俷俼丂俙傪幚峴偡傞偲丒丒丒丅俙俠偼俷俶偟側偄丅偮傑傝俠傕俷俶偟側偄丅偆傫丅俙俴倀傑偐偣偱傕傛偐偭偨丠丠丅偄傠偄傠帋偡偲丄榑棟墘嶼偺倱倧倳倰們倕偲俢倕倱倲倝値倎倲倝倧値偺抣偑摨偠応崌偼俙俠丆俠偑俷俶偟側偄偙偲偑暘偐偭偨丅俉侽俉侽偺儅僯儏傾儖偺偼俠偼僛儘傪僙僢僩偡傞偲彂偄偰偁傞偑丄俙俠偼寢壥偑斀塮偝傟傞偲彂偄偰偁傞丅僛儘傪僙僢僩偡傞偲偼彂偄偰側偄偺偱側傫傜偐偺忬懺偵曄壔偡傞偺偱偁傠偆丅幚嵺偵偳偆側傞偐偼俉侽俉侽偑柍偄偺偱暘偐傜側偄丅

偪側傒偵俢俙俙偺僥僗僩慜偱俙俠傪僋儕傾偡傞柦椷偲偟偰俷俼丂俙偲側偭偰偄傞偺偱丄俙儗僕僗僞偵壗偑愝掕偝傟偰偄偰傕摨偠僨乕僞偳偆偟側偺偱俙俠偼僋儕傾乮俷俥俥乯偝傟傞丅傕偟偐偟偨傜俉侽俉侽傕摨偠摦嶌偐傕偟傟側偄丅俷俼丂俙偲偟側偗傟偽俙俠偑僋儕傾偝傟側偄偺偐傕丅

捛婰偙偙傑偱

偱偼PROM偺僾儘僌儔儉僗僞乕僩丅OK偩両丅傛偟両傗偭偨乕乕丅弌棃偨偧両乮幚偼偸偐婌傃乯

師偵楢懕摦嶌僗僞乕僩丒丒丒丒丅偍傗丄偢偭偙偗偨丅楢懕摦嶌偺僷僗僇僂儞僩傪挷傋傞偲俁偑擖偭偰偄偨丅俁夞偼偆傑偔摦嶌偟偰係夞栚偱偢偭偙偗偨偙偲偵側傞丅

彮側偔偲傕丄侾夞偼摦嶌偡傞偺偱丄柦椷偺幚峴僔乕働儞僗偵偼栤戣側偔丄僞僀儈儞僌偵栤戣偑偁傝偦偆偱偁傞丅

僞僀儈儞僌偺栤戣偩偲擄偟偦偆偩丅

丂偝偭偦偔俴俷俧俬俠傾僫儔僀僓傪愙懕丅俫俴俿柦椷偱掆巭偡傞偺偱丄偦偙傪僩儕僈偵偡傞丅憗懍僄儔乕偱掆巭偟偨丅挷傋傞偲俠俹俬柦椷偱斾妑偟偨偲偒偵僨乕僞偼摍偟偄偺偱倅僼儔僌偑俷俶偡傞偼偢偑丄俷俶偟偰偄側偄丅倅僼儔僌偺怣崋偑傆傜偮偄偰偄傞丅偳偙偐偵傑偩敿揷晄椙偑偁傞傛偆偩丅俙俴倀偵俴俷俧俬俠傾僫儔僀僓傪愙懕偟偰嵞幚峴丄偳偆傗傜俢侾儔僀儞偑晄椙偺傛偆偩丅敿揷傪傗傝捈偟偰俷俲偲側偭偨丅

丂偝偁丄偱偼偙傟偱俷俲偐丅僥僗僩僾儘僌儔儉幚峴両丅偁傝傖偢偭偙偗偨丅偙傫偳偼偳偙偩偀乣丅傑偨傕俴俷俧俬俠傾僫儔僀僓傪愙懕丄挷傋傞偲俬俶倃柦椷偺屻偱僄儔乕偲側傞丅壗屘偵丠丠丅俬俶倃柦椷偺摦嶌傪挷傋傞偲丄俬俶倃丂俛丄俬俶倃丂俢丆俬俶倃丂俫偲幚峴偡傞偺偩偑丄偳偺柦椷偱傕俛俠儗僕僗僞偑慖戰偝傟傞丅偊偊偭乣丅俬俶倃丂俢丄俬俶倃丂俫偱俛俠傕摨帪偵慖戰偝傟傞偺偱丄僨乕僞偑働儞僇偟偰偄傞丅傗傟傗傟丅

慖戰怣崋偑懠偺慖戰怣崋偲崿怗偟偰傞偺偐側偀丅敿揷晄椙偐側偀丅偲傝偁偊偢敿揷偛偰傪摉偰偰嵞敿揷偟偰傒偨偑丄捈傜側偄丅崿怗偐傕偲巚偄丄俛俠慖戰怣崋傪弌偡強偺攝慄傪偼偢偟偰傒偨丅怣崋偼柍偔側偭偰埨掕偟偰偄傞丅崿怗偼柍偝偦偆偩偑丒丒丒偼偰丅嵞搙攝慄傪愙懕偟偨丅偍傗丄捈偭偰偟傑偭偨丅敿揷晄椙偩偭偨偺偐側偀丅偙偙傕嵞敿揷偟偰傒偨偲偙傠側傫偩偑丄晄廫暘偩偭偨丠丠丅

捈偭偰偟傑偭偰尰徾偑弌側偄偲挷傋傛偆偑側偄丅楢懕摦嶌偱昡壙傪懕偗傞偟偐側偄偐側偀丅

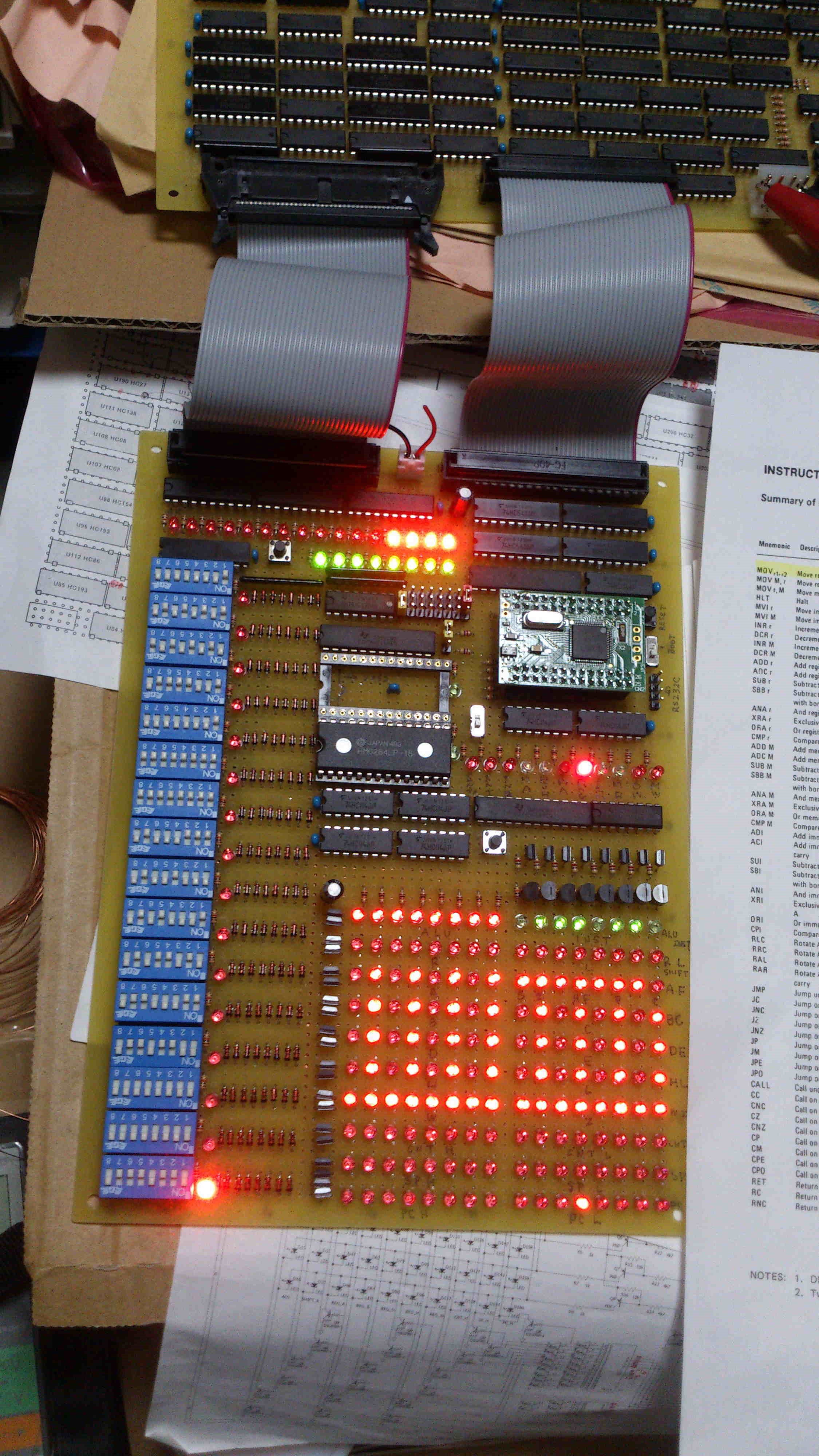

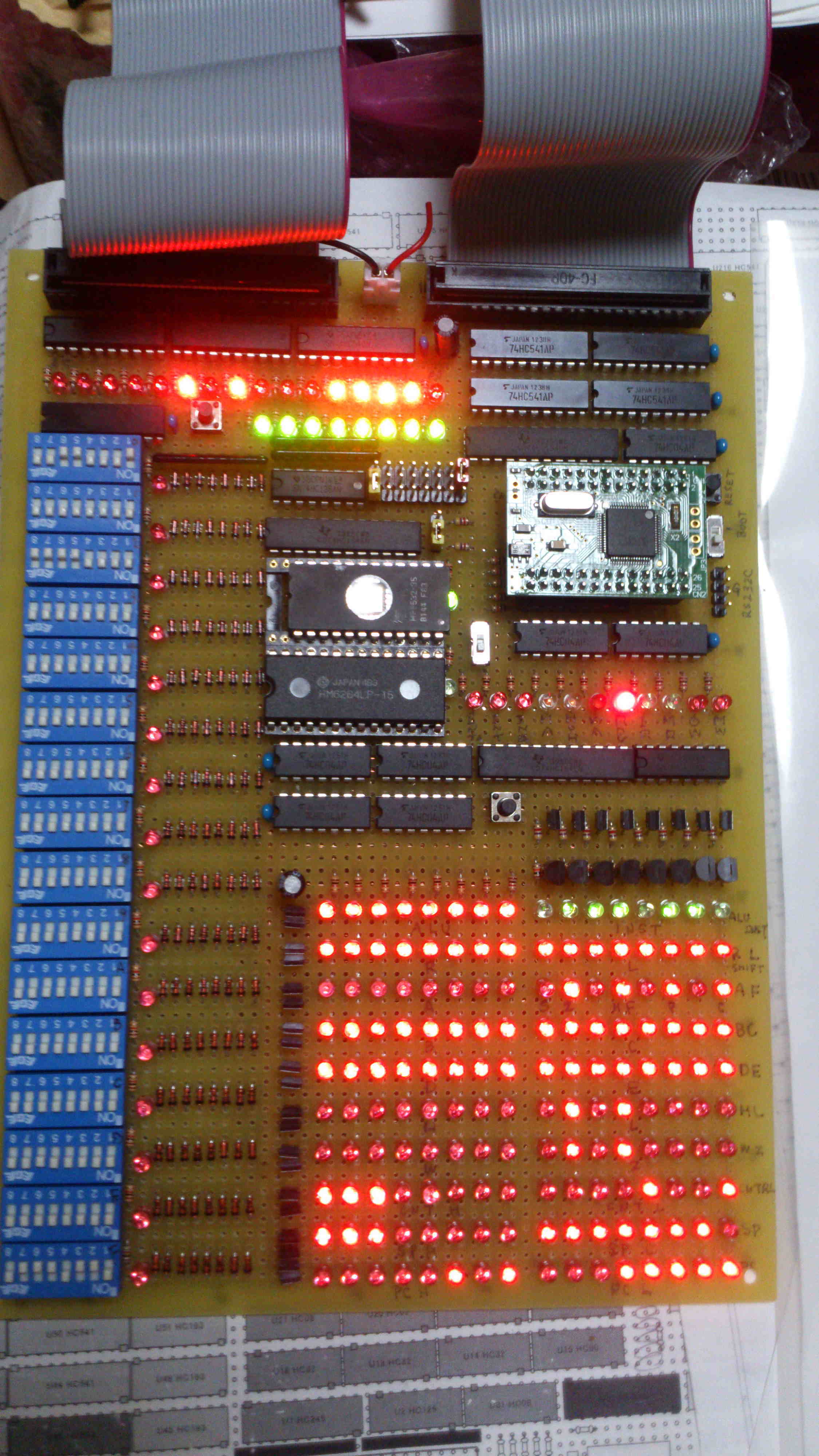

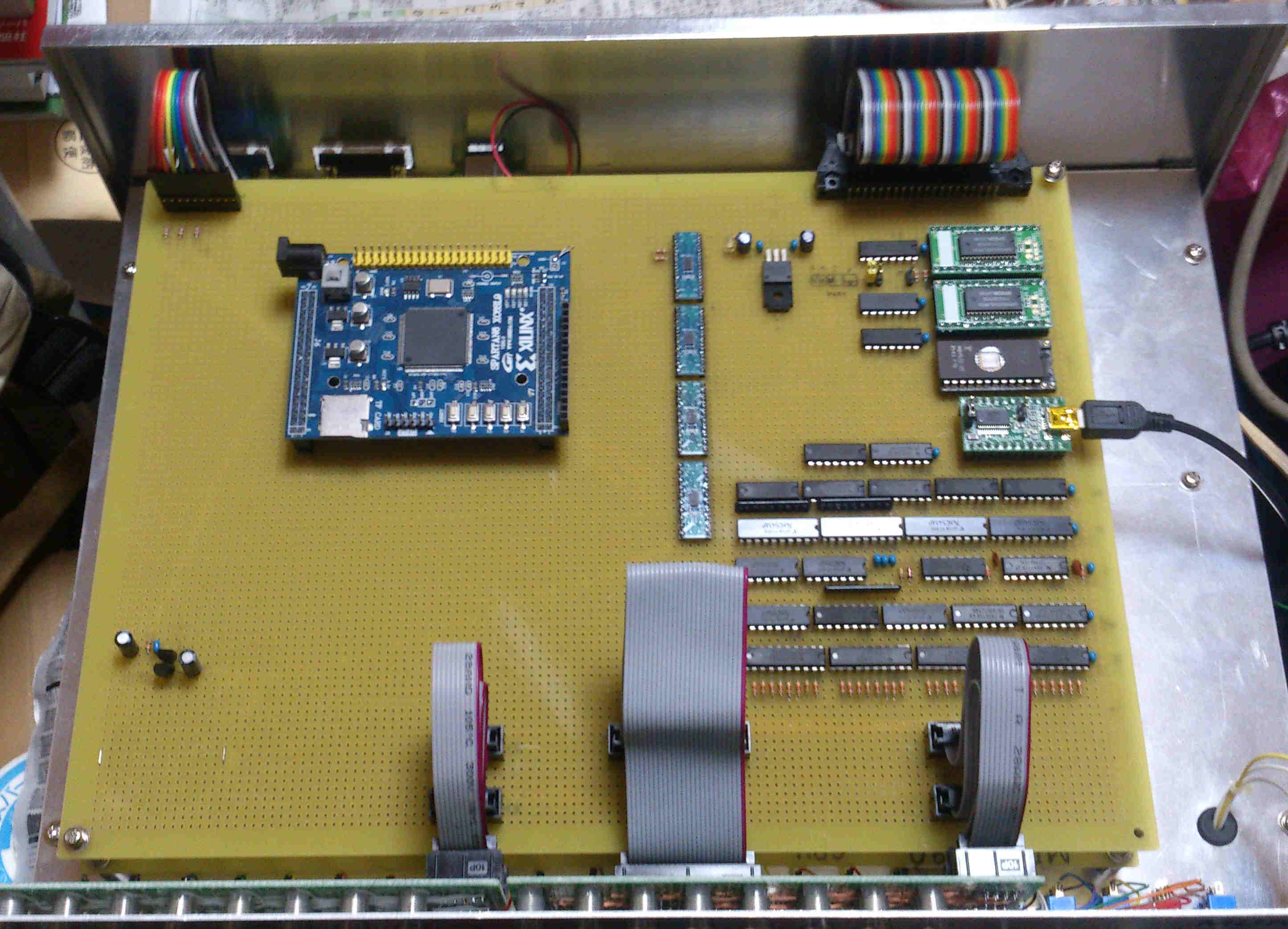

丂偝偰丄嵟廔揑偵弌棃偨昞偺晹昳搵嵹忬嫷偩丅

偪側傒偵棤懁丅攝慄偑僇僆僗忬懺丅

俼俷俵偺僥僗僩僾儘僌儔儉傪楢懕摦嶌拞丅幨恀偱偼傛偔暘偐傜傫偑丅

俀侽侾俈擭俋寧弶弡

偁偀丄偦偆偩丄俼俙俵偲俼俷俵偺僞僀儈儞僌偵偮偄偰彂偄偰側偐偭偨偺偱彮偟丅

俼俙俵偼俫俵俇俀俇係俴俹亅侾俆偱侾俆侽値倱丅摉帪偺俼俙俵偲偟偰偼抶偄曽偩丅偱傕係俵俫倸僋儘僢僋偩偲栤戣柍偄丅

俹亅俼俷俵偼俵俛俉俆俁俀亅俁俆偱偁傞丅俁俆侽値倱側偺偱丄憗偄曽偩偑丄係俵俫倸僋儘僢僋偩偲僊儕僊儕側傫偲偐撉傔傞丅

庤帩偪偺俹亅俼俷俵傪尒傞偲俵俛俉俆俁俀亅俁俆偲俵俛俉俆俁俀亅係俆偑崿嵼偟偰偄偨丅摉帪偼偁傑傝婥偵偟偰側偐偭偨偺偐側偀丅傕偆偡偭偐傝婰壇偺僇僫僞偱偁傞丅

丂偳偆傗傜楢懕塣揮偼戝忎晇偦偆偱偁傞丅偙傟偐傜廃曈婡婍偺愝寁惢嶌偱偁傞丅

丂墴擖傟偐傜屆偄暔傪敪孈偟偨丅

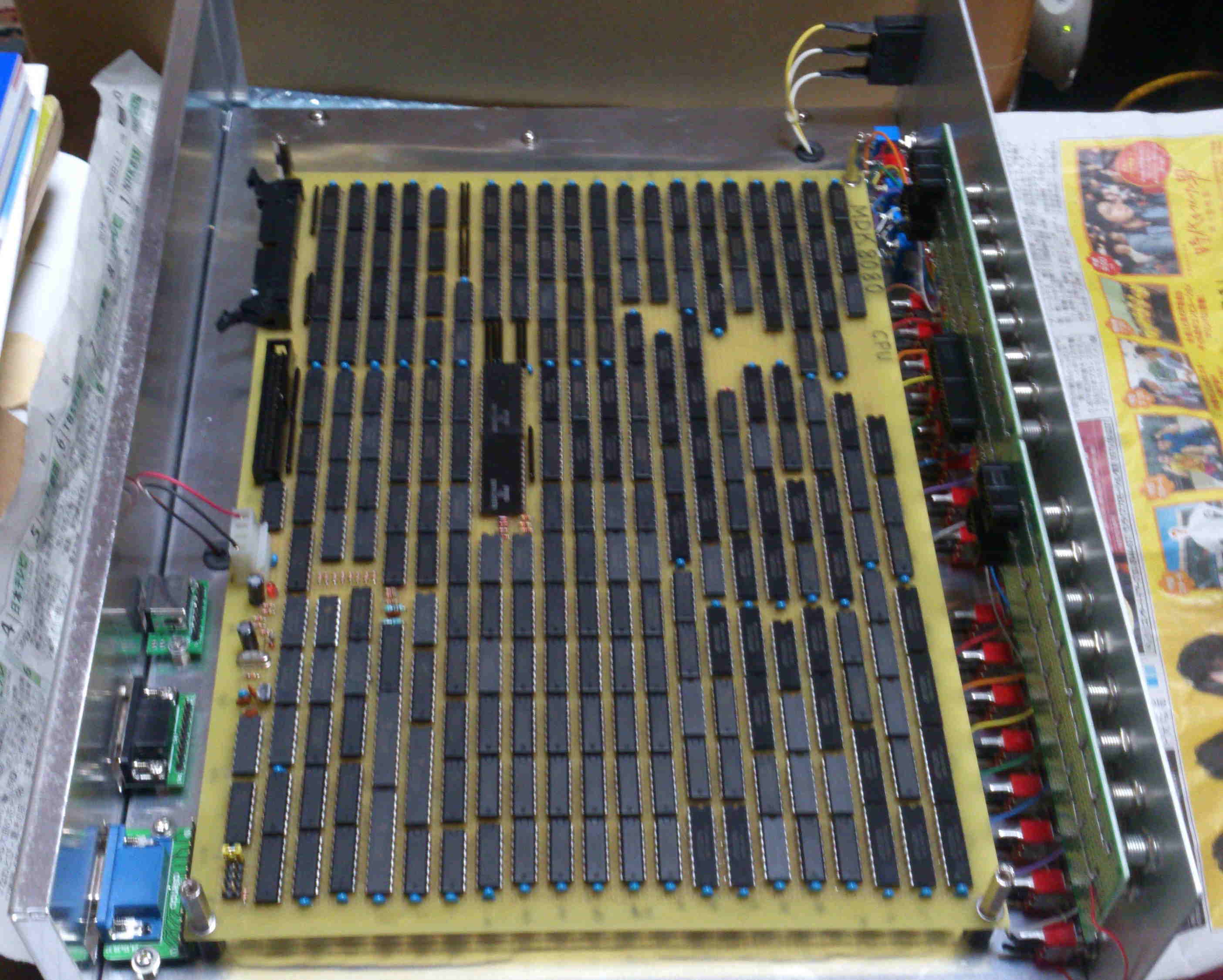

妋偐俹俠亅俇侽侽侾偺奼挘俛俷倃偐傜俛倀俽怣崋傪堷偭挘傝弌偡俬俥儃乕僪偲奼挘俵俤俵俷俼倄儃乕僪偩偭偨偲巚偆丅

偝傜偵丄偦偺奼挘偵憰拝偡傞俥俢俢僀儞僞僼僃乕僗儃乕僪偱偁傞丅

妋偐丄偙傟偱俉僀儞僠俥俢俢傪僪儔僀僽偟偰俴俷俙俢丄俽俙倁俤偟偰偄偨傛偆側丅嵍偺嵶挿偄捛壛偺儃乕僪偼屻偱捛壛偟偨僋儘僢僋惉宍夞楬偩偭偨乮偼偢乯丅

恀傫拞偺俴俽俬偑俬俶俽侾俈俈侾俶亅侾偱丄俥俢俢傪僐儞僩儘乕儖偟偰僨乕僞傪撉傒彂偒偡傞偺偩偑丄僩儔僢僋偺拞墰傛傝乮僩儔僢僋斣崋偺戝偒偄曽乯偺僨乕僞儕乕僪儈僗偑懡偐偭偨丅

偦傟傪夵慞偡傞偵偼撉傒庢偭偨僋儘僢僋攇宍傪惉宍偟偰侾俈俈侾偵擖傟傞偲夵慞偱偒傞偲壗偐偺嶨帍偵彂偄偰偁偭偨偺偱丄偦偺夞楬傪捛壛偟偨偺偩偭偨丅

偱傕丄偦傟傎偳夵慞偱偒側偐偭偨傛偆側婰壇偑偁傞丅

崱偱傕摦偔偺偐側偁丅俥俢俢偑柍偄偺偱妋擣偺偟傛偆偑柍偄丅

偁偭両偙傟傜傪巊偆偮傕傝偼偁傝傑偣傫丅崱偱偼侾僠僢僾偱俁俀倠俛偺儊儌儕偑擖庤偱偒傑偡偐傜丅偦傟偐傜俥俹俧俙傕丅

俀侽侾俈擭俋寧

丂働乕僗偵擖傟傛偆偲偟偰専摙偟偨傜丄墶暆係侽侽mm偺戝偒側働乕僗偵側偭偰偟傑偭偨丅側偵偣俠俹倀偑侾枃儃乕僪偩偐傜巇曽側偄偐側丅

丂乮僣乯偝傫偵敪拲偟偰偄偨働乕僗偑撏偄偨丅偙傟偐傜働乕僗偺壛岺偩丅

俀侽侾俈擭俋寧拞

丂僷僱儖偺壛岺傪傗偭偰偄傞丅暥帤傪偄傟傛偆偲儗僞儕儞僌傪庢傝弌偟偨傜悢帤偑側偐偭偨偺偱丄悢帤偲偮偄偱偵暥帤傕庤攝丅偲偳偔傑偱偍媥傒丒丒丒丠

俀侽侾俈擭俋寧拞

丂儗僞儕儞僌偑撏偄偨偺偱丄暥帤傪擖傟偰僋儕傾儔僢僇乕偱僐乕僥傿儞僌偟偨丅偨偩崱姡憞拞丅

偊偭両俢侾偑彮偟僘儗偰偄傞丠丅傎偐偵傕丠丒丒丒丒偊偊丄偙傟偼庤嶌傝姶傪弌偡偨傔偵傢偞偲偢傜偟丒丒丒丒丒丒丅偼偄丄晄婍梡側偺偱僘儗偰偟傑偄傑偟偨丅俢偲俹偼俉屄偟偐柍偐偭偨偺偱丄傗傝捈偣側偐偭偨偺偱偡偅両

俀侽侾俈擭俋寧枛

丂俴俤俢傪庢傝晅偗傛偆偟偨偑僶儕偑弌偰偄傞乮側傫偩偐側偀乯丅埨偄偐傜偟傚偆偑側偄偺偐傕偟傟側偄偑戝棨惢偲偄偆偺傕偁傞偐傕丅偟偐傕俴俤俢偼屻傠偐傜浧傔偰偁傞偩偗偩丅側偺偱僷僱儖偵庢傝晅偗偰傕俴俤俢傪慜偐傜墴偡偲屻傠傊敳偗偰偟傑偆偲巚傢傟傞丅

僶儕偑弌偰偄傞偺偑偍暘偐傝偐側丅偟偐傕僗僾儕儞僌儚僢僔儍乕偺傛偆側暔傕曄丄擯傝偑媡偱偁傞丅儚僢僔儍乕偲偟偰栶偵棫偨側偄乮傗傟傗傟乯丅揔摉偵宍偩偗恀帡傞偐傜偙偆側傞偺偱偁傠偆丅

俴俤俢偼屻傠傊敳偗傞丅晛捠偺朇抏宆俴俤俢偑偼傔崬傫偱偁傞偩偗丅

僶儕傪庢傞偲偒婥晅偄偨偑丄僶儕偼僇僢僞乕偱愗傝庢傟偨丅嵽幙偼垷墧乮崌嬥乯偺傛偆偱偁傞丅擔杮惢偺恀偪傘偆嶍傝弌偟偵僋儘儉儊僢僉偱偼柍偄丅

垷墧崌嬥偺傛偆側偺偱丄僱僕傪掲傔偡偓傞偲庱偺強偱攋抐偟偦偆偩丅僱僕掲傔偼婥傪晅偗側偄偲丒丒丒丅

傛偆傗偔慻傒偁偑偭偨丅

偝偰丅攝慄偟側偗傟偽丅

俀侽侾俈擭俋寧枛

丂俴俤俢偺攝慄傪僐僱僋僞愙懕偲偟偨偄偺偩偑丅俴俤俢偺儕乕僪偲僐僱僋僞傪儐僯僶乕僒儖婎斅偱愙懕偟傛偆偲偡傞偲敿揷晅偗偑棤昞偱傗傝偵偔偄丅僐僱僋僞傪愭偵敿揷晅偗偟偰俴俤俢偵婎斅傪晅偗偰敿揷晅偗偟偰傕攝慄偑丒丒丒丅偦偆偩丄俴俤俢偼屻傠偵敳偗傞偺偱丄傑偢俴俤俢傪敿揷偮偗偟偰丄俴俤俢偛偲奜偟偰僐僱僋僞傪敿揷晅偗偟偰攝慄偡傞偙偲偵偟傛偆丅

偱丄傗偭偰傒偨丅

俴俤俢傪婎斅偵敿揷晅偗偟偰丄屻傠偵敳偄偨偲偙傠丅偙偺屻僐僱僋僞傪晅偗偰攝慄偟偨丅側傞傎偳屻傠偵敳偗傞偺偼偙偺偨傔偐偀丒丒丒丒乮儂儞儅偐偄側乯丅

俴俤俢偲俽倂偺攝慄傪傗偭偰僷僱儖傪慻傫偱傒偨丅

暿偺妏搙偐傜丅

尒傟偽摦嶌偟偦偆側姶偠偩偑丄傑偩偙傟偱偼摦嶌偟側偄丅側偵偣侾枃偱俠俹倀僠僢僾偲摨摍側偺偱丄尵傢偽俠俹倀僠僢僾偩偗搵嵹偟偨傛偆側傕偺偩丅俽倂偺撉傒崬傒丄俴俤俢偺揰摂丄儊儌儕乕側偳偑昁梫偩丅

俀侽侾俈擭侾侽寧弶弡

丂僷僱儖僀儞僞僼僃乕僗偲儊儌儕乕夞楬傪塻堄惢嶌拞偩丅

俀侽侾俈擭侾侽寧拞夁偓

丂傛偆傗偔俽倂僀儞僞僼僃乕僗偲儊儌儕乕偺晹暘偑偱偒偨丅幚憰偟偰俽倂偐傜僷僠僷僠偲僾儘僌儔儉傪彂偒崬傫偱幚峴偝偣偰傒偨丅

儊儌儕偼傑偩俹俼俷俵偑弌棃偰偄側偄乮僾儘僌儔儉偑弌棃偰側偄乯偺偱俼俙俵偩偗丅俇係倠俛偺僄儕傾慡偰俼俙俵偺忬懺偩丅

偁偲丄俿俤俲俀俈俉俀偺廋棟偱梋偭偨俽俹俙俼俿俙俶亅俇偺俥俹俧俙傪嵹偣偰俽俢僇乕僪傪奜晹婰壇懼傢傝偲偡傞梊掕丅偝傜偵俽俢俼俙俵傪價僨僆俼俙俵偲偟偰僇儔乕乮俉怓乯昞帵傕偡傞偮傕傝丅偳偙傑偱弌棃傞傗傜丒丒丒丅

俼俙俵俀屄偱俇係倠俛丅偪傚偭偲僽儗偨偐側丅

庢傝姼偊偢俼倀俶丅僾儘僌儔儉偼擖偭偰柍偄偺偱朶憱忬懺丅偙偺屻俽倂偐傜彮偟僾儘僌儔儉傪僀儞僾僢僩偟偰俼倀俶偝偣偰傒偨丅愄偼偙偆傗偭偰摦偐偟偰偄偨偺偩偑丅

俀侽侾俈擭侾侽寧壓弡

丂娙扨側儌僯僞僾儘僌儔儉傪嶌偭偰俼俷俵偵從偄偨丅婡擻偼儊儌儕偺撉傒彂偒丄俬俷偺撉傒彂偒丄俫俤倃僼傽僀儖偺儘乕僪丄僽儗僀僋億僀儞僩侾偮丄儗僕僗僞昞帵丄曄峏偱偁傞丅娙扨側僨僶僢僌偼偱偒傞丅愄乆傪巚偄弌偟側偑傜惢嶌偟偨丅乮愄偺僨僶僢僌偼偙傫側傫偩偭偨傫偩傛乣乯

丂憗懍丄柦椷僥僗僩僾儘僌儔儉傪俼俙俵偱摦嶌偡傞傛偆偵彂偒姺偊丄惓忢僷僗僇僂儞僩抣傪墿怓偺俴俤俢偵昞帵偡傞傛偆偵偟偨丅俫俤倃僼傽僀儖偺嶌惉偼altair8800_emulater偱俠俹乛俵傪摦偐偟丄僐儞僷僀儖偟偰俫俤倃僼傽僀儖傪嶌傞丅偦傟傪僞乕儈僫儖僜僼僩偱棳偟崬傓丅

丂憗懍俼倀俶偝偣傞偲丄搑抂偵僄儔乕掆巭丅傫偭両壗屘偵巭傑傞丅僄儔乕偺売強傪挷傋傞偲俠俵俙柦椷偑僄儔乕偲側偭偰偄傞丅偁偁偀俢俠俼柦椷偱働儞僇偟偰偄偨偲偙傠偩丅偱傕廋惓妋擣偟偨傛側偀丒丒丒丅偭偰尵偆偐俼俷俵偺僥僗僩僾儘僌儔儉偱摦偄偰偄偨偠傖傫丒丒丒丅敿揷晄椙丠丠

丂僶儔偟偰儘僕僢僋傾僫儔僀僓傪愙懕丅傗偭傁傝敿揷晄椙偭傐偄丅俙俴倀夞傝傪擖擮偵嵞敿揷偟偨丅

丂偝偁偳偆偩丅嵞搙慻傒棫偰偰丄柦椷僥僗僩傪奐巒丅偍偍丄摦偄偨摦偄偨丅侾俆暘傎偳偟偨傜巭傑偭偨丅偊偭両丄偆乣傫丅崱搙偺僄儔乕偼俠俵俙偱偼側偄丄俠俹俬柦椷偩丅倅僼儔僌偑俷俶偟偰偄傞偼偢偑俷俶偟偰偄側偄丅偄傗乣傑偩敿揷晄椙偑丒丒丒丅

丂傑偨暘夝丅僼儔僌儗僕僗僞夞傝傪嵞敿揷丅傕偆懠偵柍偄偐丄俢俤俛倀俧儃乕僪偱僥僗僩丅摦嶌偝偣側偑傜俬俠傪巜偱僐僣僐僣偼偠偔偲摿掕偺応強偱摦嶌掆巭偡傞丅偦偺曈偵敿揷晄椙偑桳傝偦偆偩丅偦偺俬俠夞傝傪嵞敿揷丅巜偱僐僣僐僣偼偠偄偰傕摦嶌掆巭偟側偄傛偆偵側偭偨丅儎儗儎儗丅

丂偦偆偄偊偽敿揷偺傗傝曽偑慜敿偲屻敿偱堘偭偰偄傞丅俢俤俛倀俧儃乕僪偺惢嶌傛傝慜偑慜敿偱丄屻偑屻敿偱偁傞丅屻敿偱惢嶌偟偨偺偼柦椷幚峴晹偩偑丄偙偪傜偼敿揷晄椙偑偱側偄丅

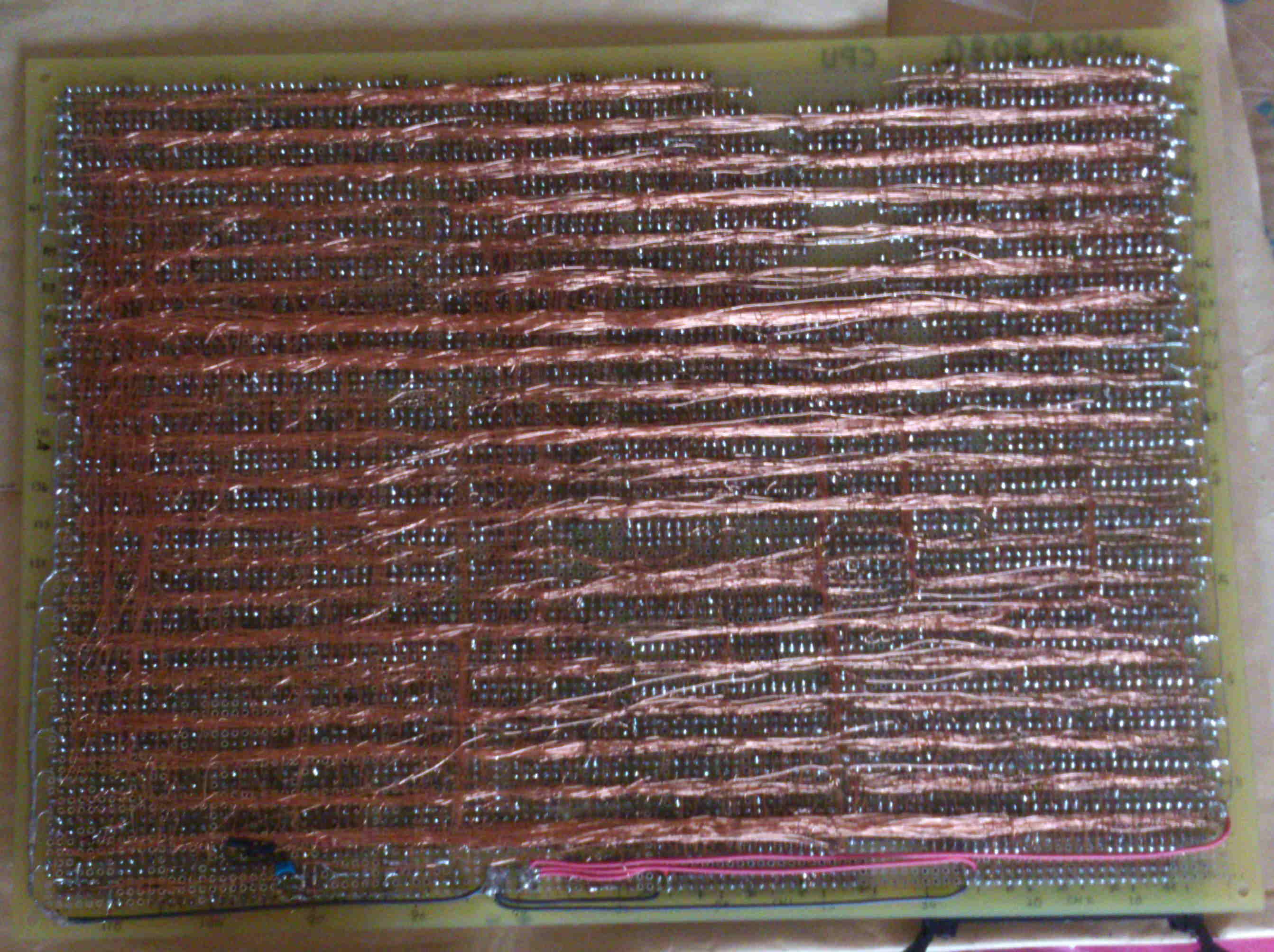

丂慜敿偺敿揷偼俬俠僺儞偵侾夞姫偒偱敿揷鑇偺擬偱旐暍傪梟偐偡傗傝曽偲丄慄偺愭抂傪敿揷儊僢僉偟偰俬俠偺僺儞傊敿揷晅偗偡傞曽朄偩偭偨丅偟偐傕敿揷鑇偺壏搙偼屻敿傛傝彮偟掅偄丅摉慠敿揷晅偗屻偵僥僗僞偱侾侽侽亾摫捠僠僃僢僋偼偟偨偺偩偑丄晅偒偑庛偄偺偐帪娫偲偲傕偵庢傟傞傛偆偩丅鑇偺壏搙偑掅傔乮旐暍傪梟偐偡偵偼乯偩偭偨偺偱旐暍偑廫暘偵梟偗側偄偺偲丄敿揷儊僢僉偟偰俬俠僺儞傊晅偗傞曽朄偼椙偝偦偆偩偑丄僺儞偺寗娫偵愭抂偑擖傝丄擖傝夁偓偰敿揷晹暘偐傜岦偙偆懁傊撍偒弌偰偟傑偭偰偄偨丅

丂俢俤俛倀俧儃乕僪惢嶌帪偵偙傟偵婥晅偄偨偺偱丄偦偺屻偼俬俠僺儞偵俀夞姫偒丄愭抂傪敿揷儊僢僉偟偨偁偲偼晅偒弌側偄傛偆偵侾夞姫偒偱敿揷晅偗偟偨丅偟偐傕敿揷鑇壏搙傪崅偔愝掕偟偨丅偟偐傕俀夞姫偔偲椡嫮偔姫偗傞偺偱丄姫偄偨偩偗偱僺儞偺妏偱旐暍偵愗傟崬傒偑偼偄傝摫捠偡傞丅偦偙傊敿揷鑇傪摉偰傞偲擬偑慄偵揱傢傝傗偡偔旐暍偑梟偗傞偺偑憗偄丅

丂慜敿偱偼摫捠僠僃僢僋偱敿揷晄椙偑尒偮偐偭偰偄偨偑丄屻敿偱偼侾侽侽亾晄椙偼偱側偔側偭偨偺偱丄屻敿偺搑拞偐傜摫捠僠僃僢僋偼徣棯偟偨丅

丂寢壥傗偼傝慜敿晹暘偱偺敿揷晄椙偑偱傞丅屻敿偐傜偼弌偰偄側偄丅

俼俷俵偲俥俹俧俙傪憰拝偟偰傒偨丅俥俹俧俙偺拞恎偼偙傟偐傜丅働乕僽儖偑宷偑偭偰偄傞偺偼倀俽俛亅僷儔儗儖曄姺婍丅嵟弶偼倀俽俛亅俼俽俀俁俀俠亅僷儔儗儖偵偟傛偆偲巚偭偰偄偨偑丄俼俽俀俁俀俠偵偡傞堄枴偑柍偄偙偲偵婥晅偒丄媫绡倀俽俛亅僷儔儗儖曄姺傪晅偗偨丅儌僯僞僜僼僩偼偙傟偱俹俠偲捠怣偡傞丅

俀侽侾俈擭侾侽寧僄儞僪

丂彂偒崬傒偑抶偔側偭偨偑丄偙偺帪婜傗偭傁傝晄嬶崌偑尒偮偐偭偨丅偦傟偼忦審俠俙俴俴柦椷偩丅忦審偑晄惉棫偱俠俙俴俴偝傟側偐偭偨帪偺嫇摦偑偍偐偟偄丅僗僞僢僋億僀儞僞乕偑侾偮尭偭偰偟傑偆丅柦椷僥僗僩僾儘僌儔儉偱偼敪尒偱偒側偐偭偨偑丄傾僾儕偱敪妎偟偨丅僒僽儖乕僠儞撪偱忦審俠俙俴俴偟偰丄晄惉棫偱栠傠偆偲偡傞偲僗僞僢僋偑嫸偭偰偄傞偺偱丄朶憱偟偨偺偩丅

尨場偼柦椷儕僙僢僩夞楬偱偁傞丅埲慜丄柦椷姰椆偱儕僙僢僩偡傞傗傝曽偱丄柦椷姰椆偺師偺僋儘僢僋偺摢偱儕僙僢僩偟偰偄傞偙偲傪彂偄偨偑丄偦傟偑嵭偄偟偰偄偨丅柦椷晄惉棫偱丄師偺僋儘僢僋偺摢偱儕僙僢僩傪妡偗傞偑丄晄惉棫偱側偄応崌偼俠俙俴俴愭傊旘傇摦嶌偲側傞丅偦偺偨傔丄尰嵼偺僾儘僌儔儉僇僂儞僞傪僗僞僢僋傊戅旔偡傞偨傔丄僗僞僢僋億僀儞僞乕傪堦偮尭傜偡摦嶌偵擖傞丅偙傟偑摨帪偵婲偙傞偺偱僗僞僢僋億僀儞僞乕偑堦偮尭偭偰偟傑偆丅

偦偙偱丄柦椷儕僙僢僩偺偲偙傠偱丄椙偄峫偊偑偁傟偽曄偊傞偐傕偲彂偄偨偑丄幚偼椙偄峫偊偑弌棃偰偼偄偨偺偩偑丄柺搢側偺偱幚巤偟偰偄側偐偭偨丅偦傟偼丄柦椷姰椆屻偺僋儘僢僋偱儕僙僢僩偡傞偺偱偼柍偔丄柦椷嵟屻偺僋儘僢僋偺偦偺嵟屻偱儕僙僢僩偡傞曽朄偱偁傞丅幚巤偡傞偵偼丄慡偰偺柦椷偺儕僙僢僩僋儘僢僋怣崋偺攝慄偑傗傝捈偟偲側偭偰偟傑偆丅庢傝姼偊偢摦嶌偟偰偄傞偺偱偦偺傑傑偵偟偰偄偨丅

偱傕丄偙偙偩偗偼偦偆偼偄偐側偄丄柦椷忦審晄惉棫偱幚峴傪僽儘僢僋偡傞庤傕偁傞偑丄峫偊偨儕僙僢僩曽朄偺専徹偺堄枴傕偁傝丄儕僙僢僩僞僀儈儞僌傪俠俙俴俴柦椷偺傾僪儗僗庢摼姰椆偺僋儘僢僋嵟屻偱儕僙僢僩偡傞夞楬偵偟偨丅寢壥偆傑偔儕僙僢僩偱偒偰摦嶌偵傕栤戣柍偄丅

懠偺柦椷慡偰偙偺曽幃偵曄偊傞偲偡偭偒傝偡傞偺偩偑丄庤娫偑丒丒丒丒丅

俀侽侾俈擭侾侾寧弶弡

丂婥晅偔偲丄夞楬愝寁傪奐巒偟偰侾擭偵側傞丅寧擔偺宱夁偼憗偄傕偺偩丅摴棟偱嵨傪偲傞偺偑憗偄偼偢偩丅庢傝姼偊偢俛俷倃偵擖偭偰摦嶌傪巒傔偨偺偱丄侾擭偱姰惉偩両両

偙傟偐傜俠俹乛俵偺堏怉偵擖傞丅俥俢俢側傫偰柍偄偐傜丄偄傗柍偔偼側偄偑俽俢俠俙俼俢側傞傕偺偑偁傞偺偱丄偙傟傪俢俬俽俲戙傢傝偵偟傛偆丅

丂憗懍丄俥俹俧俙偱俽俢俠俙俼俢傪撉傒彂偒偡傞夞楬傪嶌惉偟偰偄傞丅偄傠偄傠僱僢僩偱庤弴傪偝偖偭偰偄傞偑丄擄偟偄側偀丅

俀侽侾俈擭侾侾寧拞弡

丂俽俢俠俙俼俢偺弶婜壔偑偱偒偨偺偱丄俀俧偺俽俢俠俙俼俢傪擖傟偰帋偟偰傒偨丅偆傫丄偆傑偔丒丒丒丒丒偄偐側偄両丂丠丅

俥俹俧俙偺夞楬偼偳偆傕庢偭晅偒偵偔偄丅偮偄偮偄僜僼僩偺傛偆偵彂偄偰偟傑偆丅僴乕僪側偺偱摨帪幚峴側偺偩偑丒丒丒丅

側傫偲偐撉傒彂偒偱偒傞傛偆偵側偭偨丅傕偺偺杮偵弶婜壔僋儘僢僋偼係侽侽倠俫倸偔傜偄偲彂偄偰偁偭偨偺偱丄偦偺傛偆偵偟偰偄偨偑丄僱僢僩偱憗偔偰傕俷俲偲彂偄偰偁傞偺傪尒偮偗偨丅憗懍丄僋儘僢僋傾僢僾偟偰傒偨偑丄慡慠戝忎晇偱偁傞丅嵟廔揑偵偼侾侽俵俫倸僋儘僢僋偲偟偨丅

俀侽侾俈擭侾俀寧拞弡

丂偝傫偞傫嬯楯偟偰俽俢俠俙俼俢偺撉傒彂偒偑弌棃傞傛偆偵側偭偰丄俠俹俵偺俛俬俷俽傪嶌惉偟偨丅壗搙偐僶僌戅帯偟偰偄傞偲堦寧傎偳宱夁偟偰偟傑偭偨丅

傑偢偼俽俢俠俙俼俢偩偑庤尦偵俀俧俛偺僇乕僪偑俀枃偁傞丅1偮偼俠俵俢侽仺俠俵俢侾偱弶婜壔偱偒傞偑丄傕偆堦偮偼偦傟偱偼偩傔偱丄俠俵俢侽仺俠俵俢俉仺俠俵俢俆俆仺俙俠俵俢係侾偲偟側偗傟偽側傜側偄丅

俠俵俢俉偼偳偪傜傕桳傞偺偱丄俠俵俢侽仺俠俵俢俉仺俠俵俢俆俆傪憲偭偰儗僗億儞僗偑僄儔乕偩偭偨傜俠俵俢侾傪憲傞傛偆偵偟偨丅

俙俠俵俢係侾傪憲傜側偗傟偽側傜側偄僇乕僪偼埲慜僗儅儂偱巊偭偰偄偨偺僷乕僥傿僔儑儞傪倂倝値偲僗儅儂乮俙値倓倰倧倝倓乯偵暘偗偰偄偨偣偄側偺偐丄俵俛俼偑俀廳偵側偭偰偄偨丅

捠忢偩偲僨傿儗僋僩儕偺応強傪偨偳傞偺偵丄俵俛俼仺俛俹俛仺俥俙俿仺俢俬俼偲側傞偺偩偑丄僷乕僥傿僔儑儞傪暘偗偰偄偰丄嶍彍偟偰僼僅乕儅僢僩偟捈偟偨偵傕偐偐傢傜偢丄俵俛俼仺俵俛俼仺俛俹俛仺俥俙俿仺俢俬俼偲扝傜側偗傟偽側傜側偐偭偨丅嵟弶偺俵俛俼偱倂倝値偲俙値倓倰倧倝倓傪暘偗偰丄偦偙偐傜捠忢偺倂倝値偺俵俛俼偵側傞傛偆偩丅僼僅乕儅僢僩偟側偍偟偰傕偙偙偼巆偭偰偄偰丄倂倝値懁偺俵俛俼偱慡懱偺梕検偑巊偊傞傛偆偵側偭偰偄傞丅

丂俛俬俷俽偺僨傿僗僋僷儔儊乕僞傪俙倢倲倎倝倰俉俉侽侽倕倣倳倢倎倲倕倰偱彂偄偨僨傿僗僋僀儊乕僕偑巊偊傞傛偆偵偟偨丅俽俢俠俙俼俢偺侾僙僋僞偼俆侾俀僶僀僩偩偑俠俹乛俵偺侾僙僋僞偼侾俀俉僶僀僩側偺偱俛俬俷俽偱僶僢僼傽偟偰俼俤俙俢丄倂俼俬俿俤偡傞傛偆偵偟偨丅俼俤俙俢偼係僙僋僞枅偵俽俢俠俙俼俢偐傜撉傔偽偄偄偺偱娙扨偩偑丄彂偒崬傒偼擸傫偩偑丄彂偒偨偄僙僋僞偺俽俢俠俙俼俢偺僙僋僞傪寁嶼偟偰丄撉傒弌偟偰丄偦偺拞偺侾俀俉僶僀僩傪儊儌儕偵彂偄偰偦偺傑傑俆侾俀僶僀僩傪彂偒栠偡傛偆偵偟偨丅摨偠俽俢俠俙俼俢偺僙僋僞偱偁傟偽俀搙撉傒偼偟側偄傛偆偵偼偟偨偑丄侾俀俉僶僀僩偺彂偒崬傒偺搒搙丄俆侾俀僶僀僩彂偄偰偟傑偆丅弌棃傟偽彂偒崬傒夞悢偼尭傜偟偨偄偲偙傠偱偼偁傞偑丄庢傝姼偊偢椙偟偲偟偨丅僉儍僔儏揑偵偟偰丄俆侾俀僶僀僩僨乕僞曄峏晹偑偨傑偭偰偐傜丄傑偨偼俽俢俠俙俼俢偺堎側傞僙僋僞偺彂偒崬傒梫媮帪偵彂偒栠偡丄彂偒崬傒偑廔椆偟偨傜彂偒栠偡偺偑惓夝偐傕偟傟側偄偑丄帺暘偱巊偆偺傒側偺偱丄埨堈側曽朄偲偟偨丅

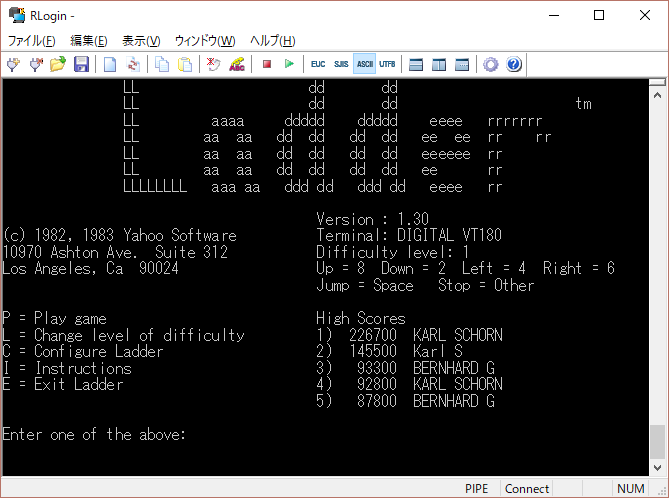

俙倢倲倎倝倰俉俉侽侽倕倣倳倢倎倲倕倰偱嶌惉偟偨僨傿僗僋僀儊乕僕偑偦偺傑傑巊偊傞傛偆偵偟偨偺偱丄偦偙偵擖偭偰偄偨傾僙儞僽儔傗俛俙俽俬俠偑偦偺傑傑堏怉偱偒偨丅

俛俷俷俿偟偰僨傿儗僋僩儕傪昞帵偟偨偲偙傠

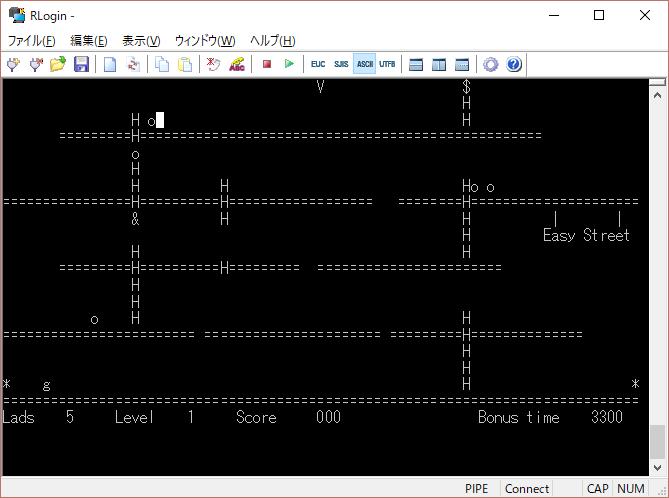

俴俙俢俢俤俼偲尵偆僎乕儉偑偁偭偨偺偱婲摦偟偰傒偨丅

偲偙傠偑丄偙偺僎乕儉傪廔椆偡傞偲俫俙俴俿偟偰偟傑偆丅嵟弶偼俛俬俷俽傪僶僌偭偨偐偲巚偭偰挷傋傞偲丄俠俠俹偺晹暘偲俛俢俷俽偺晹暘偵僷僞乕儞乮俢俙俿俙乯傪帩偭偰偄偰丄偦傟偑晄堦抳偵側傞偲俫俙俴俿偡傞丅俠俹俵俀俀偺僜乕僗偵傕僐儊儞僩偱僷僞乕儞偑堎側傞偲俫俙俴俿偡傞丄倂俫倄丠偲彂偐傟偰偄傞偺偱丄側偤偙偺傛偆側巇慻傒偵側偭偰偄傞偐媡傾僙儞僽儖偟偰僐儊儞僩傪晅偗偨摉恖偵傕暘偐偭偰偄側偄傛偆偩丅

巹偺擼枴慩側傜偸偨偩偺枴慩偱峫偊偰傒偨偑丄俠俠俹僄儕傾偺僷僞乕儞偲俛俢俷俽僄儕傾偺僷僞乕儞傪斾妑偟偰偍傝丄偳偙偵傕彂偒崬傓僾儘僌儔儉偼懚嵼偟側偄丅俠俠俹僄儕傾偼倂倎倰倣丂倐倧倧倲丂偱嵞撉傒崬傒偡傞偑丄俛俢俷俽偼撉傒崬傑側偄丅側偺偱俛俢俷俽僄儕傾偼攋夡偝傟傞偲崲傞偺偼妋偐偩偑丒丒丒丅俛俢俷俽僄儕傾偑攋夡偝傟偨偲敾掕偟偰俫俙俴俿偵偟偰丄傾僾儕奐敪幰偵抦傜偟傔傞偺偐側偁丒丒丒丅俫俙俴俿偣偢偵俠倧倢倓丂倐倧倧倲偱傕椙偝偦偆偩偑丒丒丒丠

傾僾儕偑俆俋倠俛俠俹乛俵梡偱偼柍偄偲尵偊偽偦傟傑偱偩偑丒丒丒丅

俢俬俽俲僪儔僀僽悢傪俉偵偟偨偺偱僶僢僼傽僄儕傾偵偦傟側傝偺梕検偑昁梫側偺偱丄俆俋倠偵側偭偰偟傑偭偨丅俛俬俷俽傪偱偒傞偩偗俼俷俵偵擖傟傞偲彮偟偼梕検偑憹偊偰俇侽倠俠俹乛俵偵偼弌棃偦偆偩偑丄崱屻偺壽戣偲偟偰偍偙偆丅

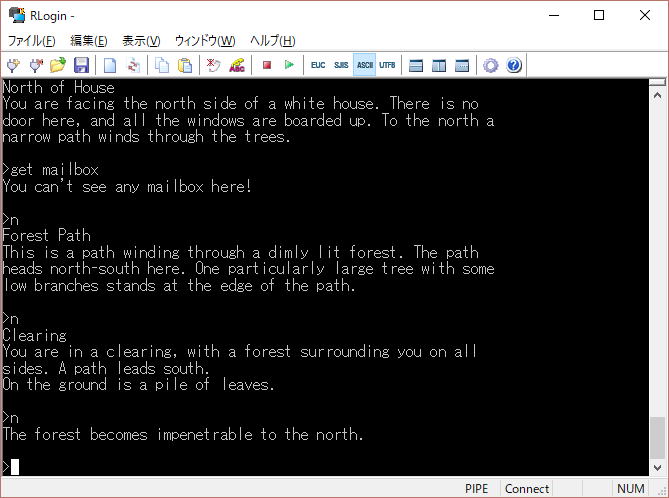

俀侽侾俉擭侾寧拞

丂婥偯偗偽俀侽侾俉擭傕敿寧偑夁偓偨丅庢傝姼偊偢俠俹乛俵偑婲摦偱偒偨偑丄傑偩嵶偐偄晹暘偑偆傑偔偄偐側偄偺傪丄摦嶌妋擣偟側偑傜廋惓偟偨丅椺偊偽丄倂俵偱僾儘僌儔儉傪曇廤偟偰廔椆偟偨偲偒偵丄昁偢俙僪儔僀僽偵栠偭偰偟傑偆丅俙僪儔僀僽偱曇廤偟偰偄傞偲婥偯偐側偐偭偨偑丄俛傗俠僪儔僀僽偱曇廤偟偰傕俙偵栠傞丅僂僆乕儉僽乕僩屻偵俠俹乛俵傊僕儍儞僾偡傞偲偒俠儗僕僗僞偵僇儗儞僩僪儔僀僽斣崋傪擖傟偰偍偐側偗傟偽偄偗側偄偺偑丄擖偭偰側偐偭偨偺偩丅側偳側偳丒丒丒丅

丂偲偙傠偑偙傟偑嵭偄偟偰偐丄懚嵼偟側偄僪儔僀僽偵愗傝懼偊偨偲偒僄儔乕偲側傞偑丄僐儞僩儘乕儖亄俠偱僂僆乕儉僽乕僩偟偰嵞傃丄僄儔乕偲側傞丅偮傑傝僇儗儞僩僪儔僀僽偺懚嵼偟側偄僪儔僀僽傊傾僋僙僗偟偰丄嵞搙僄儔乕偲側傞丅偙傟傪塱墦偲孞傝曉偡丒丒丒丅側傫偩偐側偀丒丒丒丅俠俹乛俵偺僜乕僗傪尒偰傕僐儞僩儘乕儖亄俠偱扨偵僂僆乕儉僽乕僩傊僕儍儞僾偟偰偄傞偩偗丅偆乣傫丄偳偆偡傟偽丒丒丒丒丅巄偟峫偊傛偆丒丒丒丅

俀侽侾俉擭俀寧弶

丂傗傟傗傟俀寧偵側偭偰偟傑偭偨丅

丂俥俹俧俙儃乕僪偺俢俼俙俵偵俵俢俲俉侽俉侽偐傜僨乕僞傪彂偒崬傫偱丄偦傟傪倁俧俙怣崋偱弌椡偡傞晹暘傪嶌惉偟偰偄偨丅俵俢俲俉侽俉侽偐傜僨乕僞傪彂偔偲偒偵儈僗傞偙偲偑偁傝丄偄傠偄傠挷傋傞偲丄俵俢俲俉侽俉侽偺俆倁宯偐傜俥俹俧俙偺俁丏俁倁宯偺曄姺婡婍偑岆摦嶌偟偰偄傞傛偆偩丅廐寧偱攦偭偨曄姺婡偱憃曽岦帺摦愗姺偊側偺偩偑丄僨乕僞僶僗偼憃曽側偺偱偙傟偱椙偄偑傾僪儗僗傗俬俷丄俵俤俵俷俼倄偺俼俤俙俢乛倂俼俬俿俤怣崋偼堦曽岦側偺偱帺摦愗姺偊偼晄梫偱偁傞丅傛偔挷傋傞偲僨乕僞傕晄埨掕偩丅帪乆壔偗傞丅側偺偱僨乕僞僶僗偼俈係俫俠俀係俆傪晅偗偰丄曄姺婡偑曽岦傪娫堘偭偰傕俵俢俲俉侽俉侽懁傊塭嬁偑媦偽側偄傛偆偵偟偨丅偱傕傾僪儗僗傗俼俤俙俢怣崋側偳傕塭嬁偑偁傞偺偱僶僢僼傽傪擖傟偨丅帺摦愗姺偊偼椙偝偦偆偱丄偁傑傝傛偔側偐偭偨丅堄恾偟偨曽岦偵側偭偰偔傟側偄丅

偝偰丄曽岦傪屌掕偟偨偑乮僨乕僞僶僗偼堘偆偑乯傑偩摦嶌偑偍偐偟偄丅偝傜偵挷傋傞偲俬俷倂俼俬俿俤怣崋偵僲僀僘偑嵹偭偰偄傞傛偆偩丅偆乣傫丄攝慄偺堷偒夞偟偑傑偢偄偺偐側偁丅偟傛偆偑側偄偺偱丄俥俹俧俙偱僠儍僞儕儞僌杊巭夞楬偺傛偆側夞楬偱撉傓偙偲偵偟偰偢偄傇傫偲夵慞偝傟偨丅偱傕傑偩偲偒偳偒偍偐偟偄帪偑偁傞丅傎偲傫偳栤戣側偔摦嶌偡傞偺偩偑丄朰傟偨偙傠倂俼俬俿俤怣崋傪尒棊偲偡偙偲偑偁傞丅傎偲傫偳俽俢俠俙俼俢偺撉傒弌偟僐儅儞僪偺彂偒崬傒乮倂俼俬俿俤乯傪尒摝偡偺偱丄僨乕僞俼俤俙俢偱懸偪傏偆偗偵側偭偰丄偩傫傑傝偵側傞丅懸偪傏偆偗偵側傜側偄傛偆偵娔帇僞僀儅乕傪擖傟傞偲椙偄偺偩偑丄偦偙傑偱傗偭偰偄側偄丅

傆偮偆偵梀傇偵偼偤傫偤傫栤戣側偄偐傜偩丅

倅俷俼俲傪梀傫偱傒偨丅

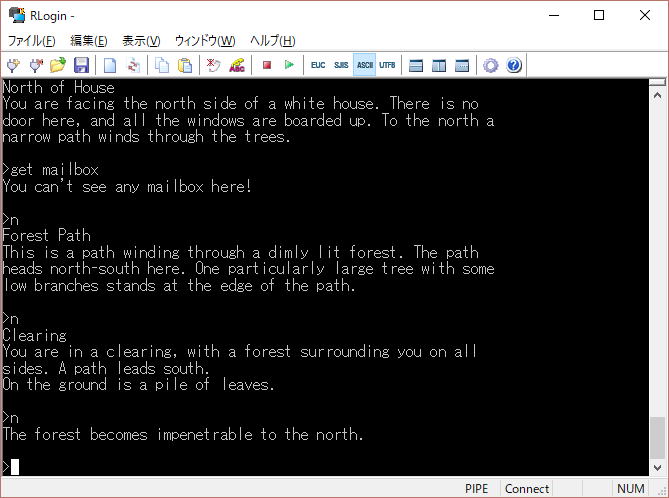

俀侽侾俉擭俁寧

丂俛俢俽丵俠傪擖庤偟偨丅愄愄攦偭偨巊偄曽偺杮傪敪孈偟偰偒偨丅偙傟偼暥朄彂偱偼側偔丄僞僀僩儖偳偍傝巊偄曽偩丅俉侽俉侽偺俠俹乛俵偱摦嶌偝偣傞愢柧偲側偭偰偄傞丅憗懍奐偄偰尒偨偑偡偭偐傝朰傟偰偄傞丅儈僗僾儕傪廋惓偟偨嵀愓偑偁傞偺偱丄摉帪丄堦強寽柦撉傫偩偺偱偁傠偆丅偑丄婰壇偺偐側偨偱偁傞丅

憗懍丄僥僗僩僾儘僌儔儉傪嶌偭偰婲摦偡傞偲丒丒丒丄摦嶌偼偆傑偔峴偔偑丄廔椆偱俫俙俴俿偡傞丅偍傗偍傗丄俴俙俢俢俤俼僎乕儉偲摨偠偩丅壗屘偩傠偆丠丠丠丅

俢俢俿傪巊偭偰僨僶僢僌偡傞偙偲偵偟偨丅

僨僶僢僌奐巒偟偰偡偖偵婥偯偄偨偑丄俇斣抧偐傜俀僶僀僩僨乕僞傪庢偭偰偒偰僗僞僢僋偵僙僢僩偟偰偄傞丅俇斣抧偼丄俛俢俷俽僐乕儖偺俆斣抧偺旘傃愭側偺偱丄俛俢俷俽偺僄儞僩儕億僀儞僩偲側偭偰偄傞丅偦偆偐偀丄俛俢俷俽偺愭摢傪僗僞僢僋偵偟偰偄傞偺偐偀丅偮傑傝俠俠俹僄儕傾偼僗僞僢僋偱夡傟傞巇妡偗偵側偭偰偄傞丅偱傕丄俛俢俷俽偺僄儞僩儕偼僺僢僞儕偺斣抧偱偼側偔俇斣抧偢傟偰偄傞丅偨偲偊偽俢俉侽俇斣抧偺條偵丄俫俙俴俿偵偡傞僠僃僢僋僷僞乕儞偼偙偺慜偺俇僶僀僩偵側偭偰偄傞丄俢俉侽侽乣俢俉侽俆偑僠僃僢僋僷僞乕儞偵側偰偄偰丄俠俠俹偵偁傞僷僞乕儞偲斾妑偟偰丄堘偭偰偄偨傜俫俙俴俿偡傞丅

偱傕偙偙傪僗僞僢僋偲偟偰巊偆偺偩偐傜丄愨懳偵夡傟傞丅偙傟偱偼俠偱嶌惉偟偨僾儘僌儔儉傪摦嶌偝偣傞偲昁偢俫俙俴俿偡傞偙偲偵側傞丅傗傟傗傟偩丄俠俹乛俵傪夵憿偟偰俫俙俴俿偣偢偵侽斣抧傊僕儍儞僾偝偣傛偆偐丄偦偆偡傞偲僂僆乕儉僽乕僩偡傞偼偢丒丒丒丒丅偠傖側偄丄俫俙俴俿偡傞偺偼僂僆乕儉僽乕僩偺屻側偺偱丄偦傫側偙偲偡傞偲僂僆乕儉僽乕僩傪孞傝曉偡偩偗偱偁傞丅

偆乕乕傫丄偟傚偆偑側偄丄俛俢俷俽偺愭摢侾僙僋僞傪僂僆乕儉僽乕僩偱撉傒崬傓偙偲偵偟傛偆丅

偦偙偱丄僂僆乕儉僽乕僩傪夵憿偟偰俼俷俵傪從偒捈偟偨丅憗懍偨傔偡偲丒丒丒丒丅偆傑偔峴偭偨両丅傛偟両

偙傟偱俴俙俢俢俤俼偺廔椆傕偆傑偔峴偔傛偆偵側偭偨丅

偮偯偔

丂

丂